# VHDL

### DESIGN, SYNTHESIS, AND SIMULATION

### Debaprasad Das

Professor and Head Department of Electronics and Communication Engineering Assam University Silchar

© Oxford University Press. All rights reserved.

#### OXFORD

UNIVERSITY PRESS

Oxford University Press is a department of the University of Oxford. It furthers the University's objective of excellence in research, scholarship, and education by publishing worldwide. Oxford is a registered trademark of Oxford University Press in the UK and in certain other countries.

Published in India by Oxford University Press Ground Floor, 2/11, Ansari Road, Daryaganj, New Delhi 110002, India

© Oxford University Press 2018

#### The moral rights of the author/s have been asserted.

First published in 2018

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, without the prior permission in writing of Oxford University Press, or as expressly permitted by law, by licence, or under terms agreed with the appropriate reprographics rights organization. Enquiries concerning reproduction outside the scope of the above should be sent to the Rights Department, Oxford University Press, at the address above.

> You must not circulate this work in any other form and you must impose this same condition on any acquirer.

> > ISBN-13: 978-0-19-809329-9 ISBN-10: 0-19-809329-2

Typeset in AGaramondPro-Regular by MacroTex Solutions, Chennai Printed in India by Magic International (P) Ltd., Greater Noida

Cover image: VLADGRIN / Shutterstock

Third-party website addresses mentioned in this book are provided by Oxford University Press in good faith and for information only. Oxford University Press disclaims any responsibility for the material contained therein.

## Features of

**Example 11.8.** Write a VHDL testbench program to read the input bit patterns from a file "fa2.vec" and generate the input waveforms, simulate the design and write the simulated input/ outputs into another file "fa2.out". library ieee, std;

use ieee.std\_logic\_1164.all; use ieee.std\_logic\_textio.all; use std.textio.all;

> 🗍 fa2 - Notepad File Edit Format View Help Simulation results of full-adder: Simulated Expected outputs Inputs outputs Time АВС | Cout Sum Cout Sum 1 Time = 0 ns Time = 10 ns Time = 20 ns Time = 30 ns Time = 40 ns Time = 50 ns Time = 50 ns0 0 0 0 0 0 0  $\begin{array}{c}

>  0 & 0 & 0 \\

>  0 & 0 & 1 \\

>  0 & 1 & 0 \\

>  0 & 1 & 1 \\

>  1 & 0 & 1 \\

>  \end{array}$ 000101110 0 000101110 0 1010010 10 ōō  $1 0 0 \\ 1 0 1$ 100  $\begin{array}{c}

>  1 & 0 & 1 \\

>  1 & 1 & 0 \\

>  1 & 1 & 1 \\

>  0 & 0 & 0 \\

>  \end{array}$ Time = 100 ns = 110 ns 001010 0 Simulation completed. FIGURE 11.10 Content of fa2.out file

#### Solved Examples

The book comprises various solved examples to provide readers with a deep understanding of the concepts discussed in the chapters.

#### Appendices

Appendices A, B, C, and D are provided at the end of the book for readers to gain additional knowledge. Appendix A discusses design with Xilinx FPGA, B covers lab exercises, C consists of some mini projects, and D includes versions of VHDL-87 and 93.

Material based on or adapted from figures and text owned by Xilinx, Inc., courtesy of Xilinx, Inc. © Copyright Xilinx [2018].

## the Book

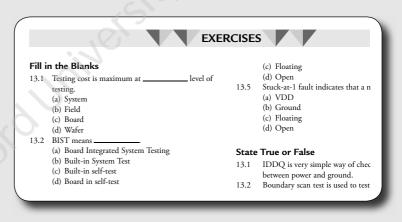

#### **Chapter-end Exercises**

The book covers enough chapter-end exercises, such as fill in the blanks, multiple choice questions, true or false, short-answer type questions, and long-answer type questions for readers to test their knowledge.

#### SUMMARY

- Verification is the process of checking the circuit while it is being designed.

- Cost of testing increases exponentially as moved from the wafer level to the field level.

The further in 100 and the research strains

- The faults in ICs are due to manufacturing defects of ICs. These are modeled to identify different types of fault.

- The most popular fault models are stuck-at-1 and stuck-at-0 faults.

- Scan test uses scan flip-flop has a other than normal input. When be scanned, scan input is selected

- 6. Boundary scan test is used to tes the board level.

- 7. Built-in self-test introduces extra chip for testing purpose.

- 8. Yield is the ratio of defect-free c total number of chips manufactu

#### Summary

The chapter-end summary presents all the important concepts explained in the chapter in the form of points. This helps to provide a quick grasp of concepts learnt in each chapter.

## Preface

VHDL is a hardware description language that is extensively used for design, synthesis, and simulation of digital logic circuits. The language is different from other programming languages in that it supports the most important feature of concurrent statements. In normal programming languages, the statements are executed sequentially, however, in VHDL the statements can be executed concurrently. VHDL is very popular in both academics as well as industry.

VHDL is a case insensitive language. It has a syntax and certain keywords similar to other programming languages, and can support different data types and data objects. It also supports different modelling styles dataflow, behavioural, structural, and mixed. These modelling styles are provided in order to support the different levels of hardware abstraction.

I have always thought that there should be a book on VHDL in which the purpose of the book will not be just to learn the language but to learn how to design using VHDL. Therefore, I have designed the book from the perspective of digital design techniques.

After going through the basics of writing codes in VHDL, students will be able to design efficient programs too since the book has a lot of programming examples and exercises. The students will also develop a basic understanding about digital logic circuits and the concepts of hardware design.

#### ABOUT THE BOOK

*VHDL: Design, Synthesis, and Simulation* is designed as a textbook for undergraduate students of electronics and communication engineering, computer science and engineering, and information technology, as well as postgraduate students of computer applications. It will also help the students of allied engineering disciplines. The objective of the book is to introduce the concepts of digital logic design, and then help students apply these concepts in VHDL programs and develop applications for real world problems. Starting with basic logic gates, the book explains how to design logic circuits up to the complexity of a central processing unit. This will help students to get used to the techniques and applications of VHDL. After discussing digital logic circuits, the book then elucidates the basics of hardware description language. It is also useful as a reference and resource to professional hardware designers working on VHDL and other similar languages.

It explains the primary and basic constructs, data objects, data types, operators, various modelling styles and different statements, functions, procedures, attributes, and configurations in subsequent chapters. Different modelling styles are presented with the concepts on how to choose and when to use which modelling style. Different types of statements are discussed with suitable examples so that the students understand the applicability of the statements for different applications. Delay modelling is presented for gate delay and interconnect delay. Verification of logic circuits and testing methodologies are discussed. Numerous design examples including memory, finite state machines, arithmetic logic unit (ALU), and microcontroller are provided to explain the design concepts behind developing systems with higher complexity. Design with programmable logic devices, field programmable gate array, and complex programmable logic device are included so that students can understand the concepts of system level realization. Writing testbench programs is explained in a separate chapter with a variety of approaches for developing testbench programs for testing the digital logic circuits. A separate chapter on Verilog HDL is provided at the end to help students port already written VHDL programs for a system into Verilog programs, if the situation demands so.

In order to further improve the understanding of the subject, numerous objective and subjective type questions, and programming exercises are provided at the end of each chapter.

#### **KEY FEATURES**

- *Simple and lucid explanations* for basic concepts of digital logic design using illustrations and examples for easy understanding

- A lot of compiled and tested *programs along with their outputs* to help students improve their programming skills

- Case studies within the text to demonstrate the implementation of the concepts learnt in various chapters

- Numerous *chapter-end exercises* including fill in the blanks, true/false, multiple choice questions with answers, short-answer type questions, and long-answer type questions for self-check and practice

- Point-wise *summary* at the end of each chapter and *Glossary* of key terms at the end of the book to help students quickly revise the important concepts

#### ORGANIZATION OF THE BOOK

The book is divided into 21 chapters and 4 appendices.

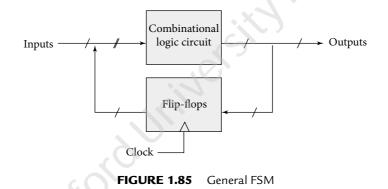

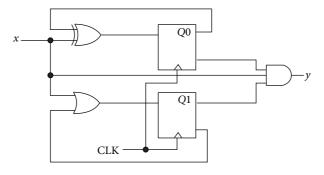

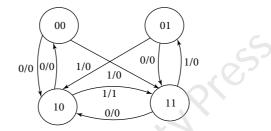

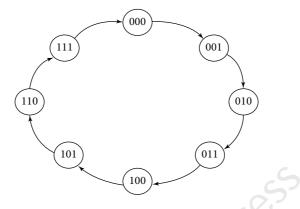

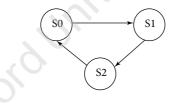

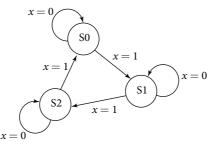

**Chapter 1** provides an introduction to digital logic design. For a brief recapitulation of the students, the Boolean algebra, basic logic gates, and different combinational and sequential logic circuits are discussed. After that the finite state machines, memory, and control logic are discussed. Finally, the basics of algorithmic state machine is also explained in the chapter.

**Chapter 2** is the introduction to VHDL language. It starts with the historical background of development of VHDL followed by basic language syntax. Then it presents data objects, data types, and operators supported by the language. Different hardware modelling styles are discussed next. Various statements such as concurrent statements, sequential statements, different control and looping statements, signal and variable assignments, block statement, etc. are discussed in this chapter.

*Chapter 3* deals with the dataflow modelling of the digital logic circuits. After introduction, it presents dataflow modelling of basic logic gates, followed by different combinational logic circuits. It also presents dataflow modelling using block statements. Finally, dataflow modelling of multiplier and divider is presented.

**Chapter 4** deals with behavioural modelling. The concept of behavioural modelling with the help of sequential statements is presented in this chapter. Starting with combinational logic circuits, the sequential logic circuits such as shift registers, counters, and memory design using behavioural modelling is explained with suitable examples. The chapter ends with the design of ALU and traffic light controller example.

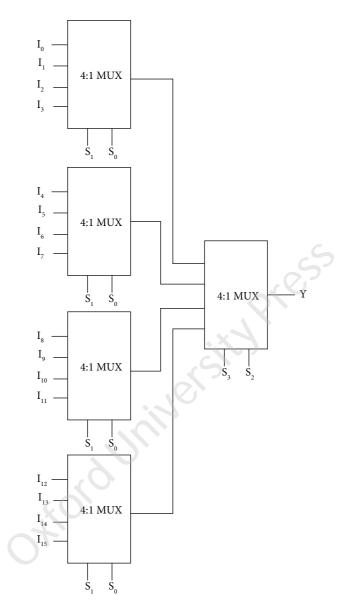

*Chapter 5* presents the structural modelling of digital logic circuits. It discusses the hierarchical description using component declaration and instantiation. Logic circuits at a higher level such as adder, subtractor, multiplier, shift register, barrel shifter are discussed. Design of bigger size multiplexer/decoder using smaller size multiplexer/ decoder is presented at the end.

*Chapter 6* discusses the mixed modelling style which is a combination of dataflow, behavioural, and structural modelling styles. Several examples of mixed modelling styles are presented to explain the necessity of such a style.

**Chapter** 7 deals with concurrent statements. It presents block statement, process statement, procedural call statement, signal assignment statement, assertion statement, component instantiation statement, and generate statement with suitable examples.

**Chapter 8** deals with sequential statements. It presents wait statement, report statement, different types of signal assignment statements, and different types of variable assignment statements, if, case, loop, exit, next, return, and null statements.

**Chapter 9** introduces the advanced features of VHDL. It discusses several attributes, group, configuration, subprogram, procedure, operator overloading, alias declaration, signatures, guarded signal, and qualified expression.

*Chapter 10* presents the design of ALU. It first illustrates the concept with the help of 1-bit ALU, then it discusses the behavioural design of 16-bit ALU followed by structural design of ALU. Each of the individual blocks is designed first and finally, the blocks are integrated to design the ALU.

**Chapter 11** elucidates on model simulation. After all these chapters, the students must learn how to verify the functionality of the design. It introduces the concept of testbench and then generation of input stimulus using different schemes. It also presents how to check the outputs. Different types of testbench are presented with examples. Finally, it discusses event driven simulation and cycle based simulation techniques.

*Chapter 12* introduces delay modelling in VHDL. It explains the two kinds of delay in digital circuits- delay associated with logic gates called delay, and delay associated with interconnects/wires called interconnect delay. The chapter presents how effectively these two kinds of delay can be modelled in VHDL. Finally, the setup and hold time checks of a sequential element are also discussed.

*Chapter 13* introduces the concepts of verification and testing of digital logic circuits. Several verification methods such as simulation, formal verification, and static timing analysis have been discussed. Next the testing of logic circuits, fault models, different testing techniques, and algorithms are presented in this chapter.

**Chapter 14** is about synthesis of digital logic circuits. It is basically to explain the process of implementing the design on a FPGA chip. The examples of different synthesis illustrate the idea behind the allocation of resources available in FPGA system. Different constraints used for synthesis are also discussed.

**Chapter 15** presents placement and routing techniques. When design is synthesized, it is then mapped to the available logic blocks and then routing is done to make the interconnections between the logic blocks. Different placement and routing algorithms are explained in this chapter.

*Chapter 16* elucidates the file handling features of VHDL. It explains how to declare a file, and open and close a file. The reading and writing procedures are explained with suitable examples. File handling capability is mainly useful for writing testbench programs.

**Chapter 17** is all about floating point arithmetic. It explains different number system representations and then how to represent floating point numbers. The operations such as addition and multiplication with floating point numbers are discussed with suitable examples.

*Chapter 18* discusses the basics of programmable logic devices such as PLD, SPLD, CPLD, and FPGA. It explains the architecture of basic FPGA and CPLD devices. Finally, it describes the process of FPGA based digital design.

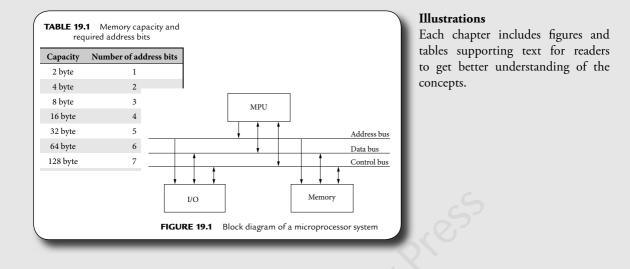

*Chapter 19* discusses the modelling of memory and bus. Different types of memories such as ROM, RAM, SRAM, DRAM, and Dual port RAM are discussed. The concept of buses and modelling of buses is discussed with suitable examples.

*Chapter 20* presents several design examples. It starts with different types of multiplier, followed by divider, then memory, and state machines. The concept of microprogramming, UART design, design of microcontroller, and finally a vending machine are explained with VHDL programs.

*Chapter 21* is the last chapter of the book and explains Verilog. Verilog is another hardware description language (HDL). To give the students a flavour of the language, basic features of Verilog, different types of modelling and statements, and a few examples are provided.

#### **x** Preface

The four appendices namely, *Appendix A* discusses the design with Xilinx FPGA, *Appendix B* includes some laboratory exercises, *Appendix C* provides a few mini projects, and *Appendix D* covers versions of VHDL: 87 and 93.

#### **ONLINE RESOURCES**

To help teachers and students, the book is accompanied with the following online resources that are available at http://oupinheonline.com/book/das-VHDL/9780198093299:

For Faculty

• Chapter-wise PPTs

- For Students

- Some important codes from different chapters

- Chapter-wise solutions for select problems

#### ACKNOWLEDGMENTS

I am blessed to have great teachers during my undergraduate and postgraduate studies from Contai P. K. College, Institute of Radiophysics and Electronics, Jadavpur University, and Indian Institute of Engineering Science and Technology (formerly Bengal Engineering and Science University), Shibpur, who have always been a great inspiration in my life. I am also fortunate to have had great colleagues while working in Texas Instruments, Bangalore and Meghnad Saha Institute of Technology, Kolkata, who were always supportive of my decisions. It is my pleasure to express my heartfelt indebtedness to all of them.

The writing of this textbook was a challenging task for which a lot of help was required from many people. Fortunately, I have had the fine support of my family, friends, and fellow members of the teaching and non-teaching staff at the Triguna Sen School of Technology, Assam University, Silchar.

I pay my tribute to my parents, Smt. Pratima Das and (Late) Sri Birendranath Das, who were a source of abiding inspiration and divine blessings for me. I am especially thankful to my wife, Joyita, and my loving daughters Adrija and Adrisha, who have been very patient and cooperative in letting me realize my dreams. My sincere thanks to all my dear students, friends, and all well-wishers, for their inspiration in writing this book.

Last but not the least, I thank the editorial team at Oxford University Press, India for their help and support.

Your comments and suggestions for the improvement of the book are welcome. You can connect with me at dasdebaprasad@yahoo.co.in.

**Debaprasad Das**

## **Brief Contents**

Preface vii Features of the Book iv Detailed Contents xii

| 1.   | Introduction to Digital Logic Design | 1   |

|------|--------------------------------------|-----|

| 2.   | Introduction to VHDL                 | 77  |

| 3.   | Dataflow Modeling                    | 114 |

| 4.   | Behavioral Modeling                  | 141 |

| 5.   | Structural Modeling                  | 161 |

| 6.   | Mixed Modeling                       | 192 |

| 7.   | Concurrent Statements                | 202 |

| 8.   | Sequential Statements                | 215 |

| 9.   | Advanced VHDL                        | 228 |

| 10.  | Arithmetic Logic Unit Design         | 273 |

| 11.  | Model Simulation                     | 298 |

| 12.  | Delay Modeling                       | 322 |

| 13.  | Verification and Testing             | 344 |

| 14.  | Synthesis                            | 370 |

| 15.  | Place and Route                      | 396 |

| 16.  | File I/O                             | 402 |

| 17.  | Floating-point Arithmetic            | 415 |

| 18.  | Design with FPGA and CPLD            | 426 |

| 19.  | Memories and Buses                   | 437 |

| 20.  | Design Examples                      | 454 |

| 21.  | Introduction to Verilog              | 510 |

| Appe | ndir A. Decian with Viling EPCA 539  |     |

Appendix A: Design with Xilinx FPGA 539 Appendix B: Lab Exercises 554 Appendix C: Mini Projects 565 Appendix D: Versions of VHDL: 87 and 93 576 References 583 Index 585

## **Detailed** Contents

Preface vii Features of the Book iv Brief Contents xi

| 1. | Intro | oduction to Digital Logic Design 1    |

|----|-------|---------------------------------------|

|    | 1.1   | Introduction 1                        |

|    | 1.2   | Boolean Algebra 3                     |

|    |       | 1.2.1 Boolean Theorems 3              |

|    | 1.3   | Basic Logic Gates 3                   |

|    |       | 1.3.1 NOT Gate 4                      |

|    |       | 1.3.2 AND Gate 4                      |

|    |       | 1.3.3 OR Gate 5                       |

|    |       | 1.3.4 XOR Gate 5                      |

|    |       | 1.3.5 NAND Gate 6                     |

|    |       | 1.3.6 NOR Gate 7                      |

|    |       | 1.3.7 XNOR Gate 7                     |

|    |       | 1.3.8 Universal Gates 8               |

|    |       | 1.3.9 AND-OR-INVERT (AOI) Gate 11     |

|    |       | 1.3.10 OR-AND-INVERT (OAI) Gate 11    |

|    |       | 1.3.11 Buffer Gate 11                 |

|    |       | 1.3.12 Tri-state Logic Gate 12        |

|    |       | 1.3.13 Multi-bit Tri-state Buffer 13  |

|    |       | 1.3.14 Bus 14                         |

|    |       | 1.3.15 Bus Holder Circuit 14          |

|    |       | 1.3.16 Bidirectional Buffer 15        |

|    | 1.4   | Combinational Logic Circuits 15       |

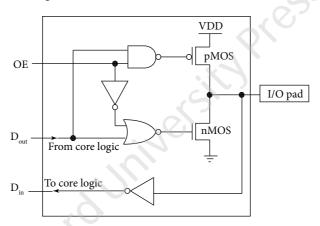

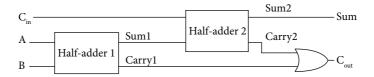

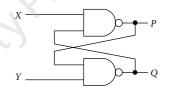

|    |       | 1.4.1 Half-adder 16                   |

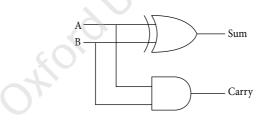

|    |       | 1.4.2 Full-adder 16                   |

|    |       | 1.4.3 Full-adder using Half-adders 17 |

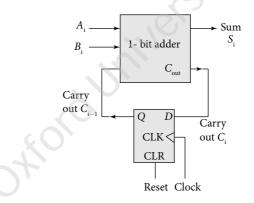

|    |       | 1.4.4 n-Bit Serial Adder 18           |

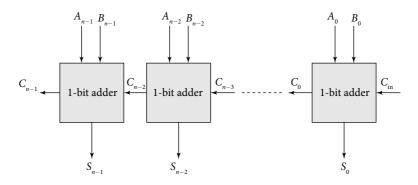

|    |       | 1.4.5 n-Bit Parallel Adder 18         |

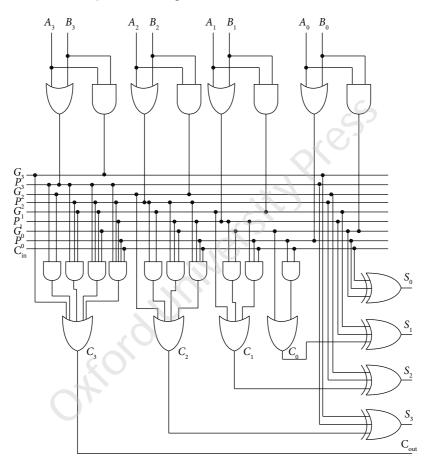

|    |       | 1.4.6 Carry Look-ahead Adder 19       |

|    |       | 1.4.7 Subtractor 20                   |

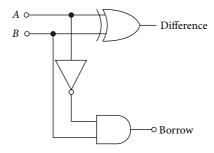

|    |       | 1.4.8 Half-subtractor 21              |

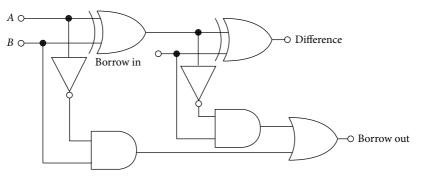

|    |       | 1.4.9 Full-subtractor 22              |

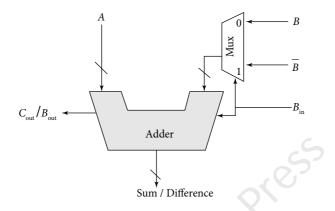

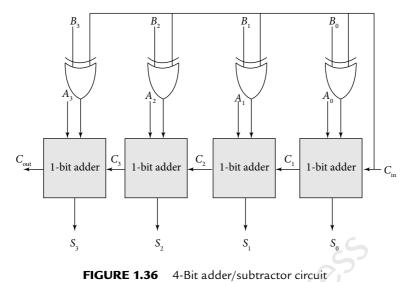

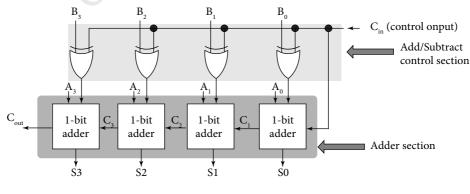

|    |       | 1.4.10 Adder/Subtractor Circuit 23    |

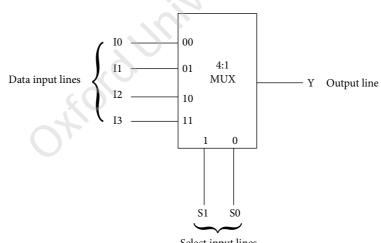

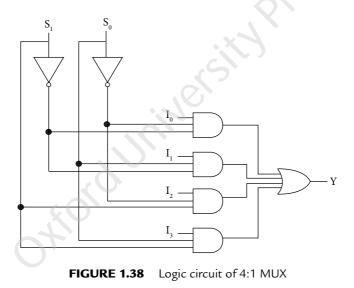

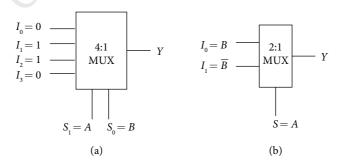

|    |       | 1.4.11 Multiplexer 24                 |

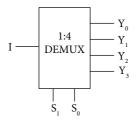

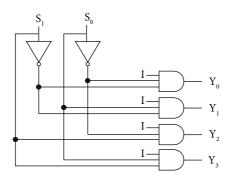

|    |       | 1.4.12 Demultiplexer 28               |

|    |       |                                       |

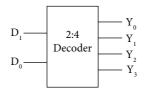

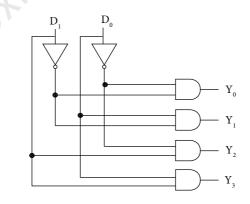

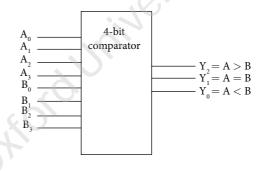

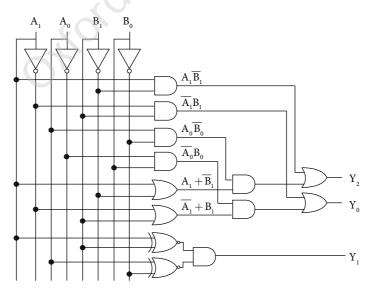

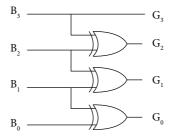

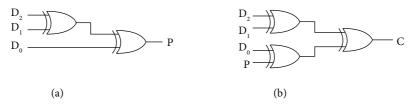

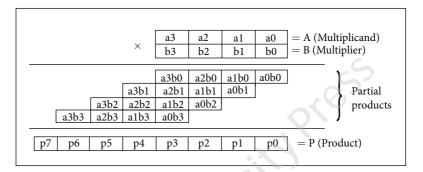

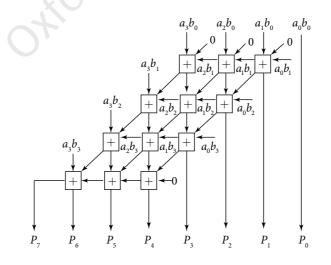

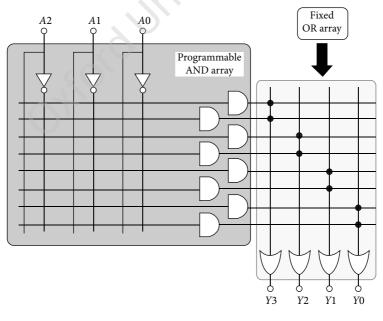

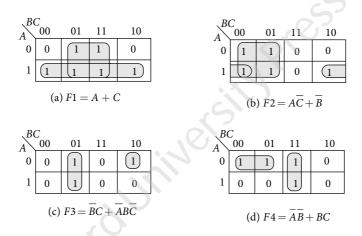

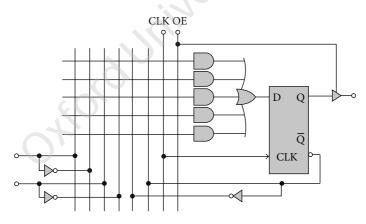

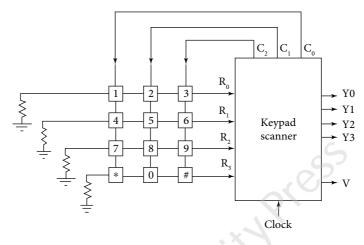

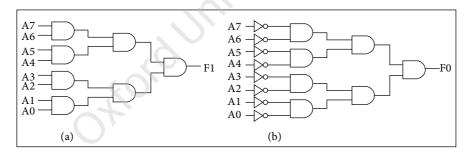

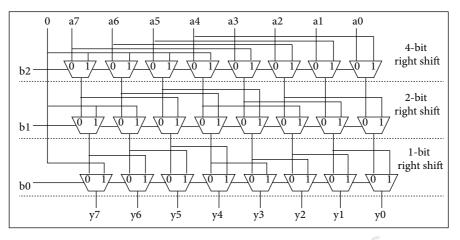

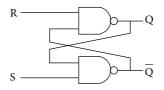

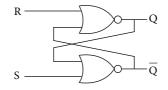

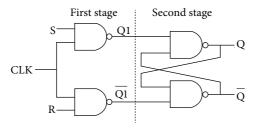

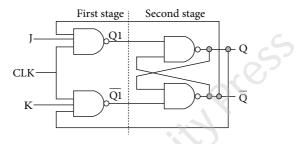

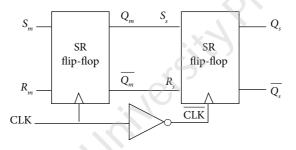

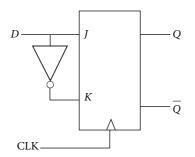

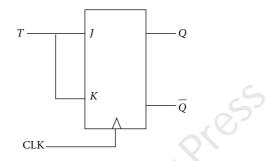

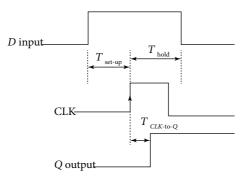

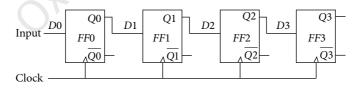

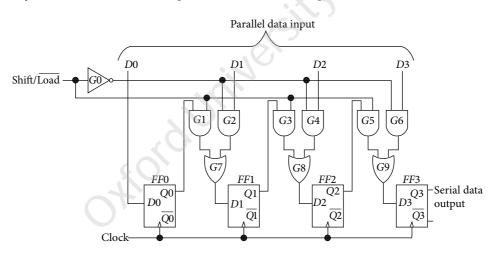

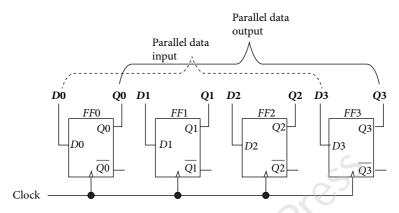

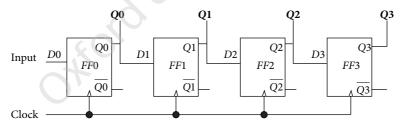

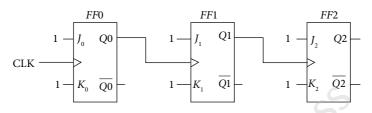

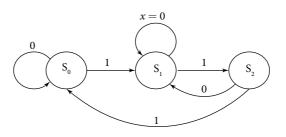

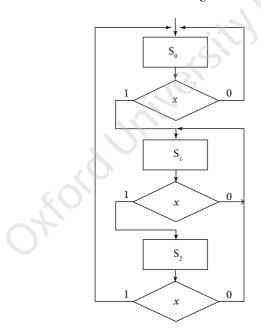

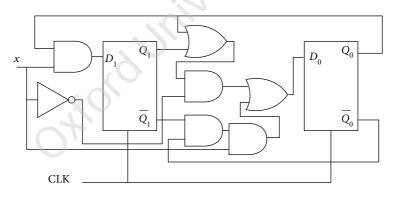

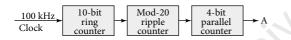

1.4.13 Decoder 29 1.4.14 Encoder 30 1.4.15 Comparator 31 1.4.16 Code Converter 33 1.4.17 Parity Generator and Checker 34 1.4.18 Array Multiplier 36 1.4.19 Programmable Logic Device 37 1.4.20 Sequential PLD 42 1.4.21 Keypad Scanner 43 1.4.22 Features of PLD 45 1.4.23 One/Zero Detector 45 1.4.24 Barrel Shifter 45 1.5 Sequential Logic Circuits 46 1.5.1 SR Flip-flop 47 1.5.2 SR Flip-flop with Clock Input 48 1.5.3 JK Flip-Flop 49 1.5.4 Master-slave Flip-flop 50 1.5.5 D Flip-flop 50 1.5.6 T Flip-flop 51 1.5.7 Flip-flop Characteristics 51 1.5.8 Registers 52 1.5.9 Shift Register 52 1.5.10 SISO Shift Register 53 1.5.11 PISO Shift Register 53 1.5.12 PIPO Shift Register 54 1.5.13 SIPO Shift Register 54 1.5.14 Counters 54 1.5.15 Asynchronous/Ripple Counter 55 1.5.16 Synchronous Counter 56 1.6 Finite-State Machine 57 1.6.1 Example of FSM 57 1.6.2 Design of an FSM 59 1.6.3 State Reduction 61 1.6.4 State Encoding 63

|      | 1.6.5 State Assignment 64                                      | 2 |

|------|----------------------------------------------------------------|---|

|      | 1.6.6 Moore Machine 64                                         |   |

|      | 1.6.7 Mealy Machine 64                                         |   |

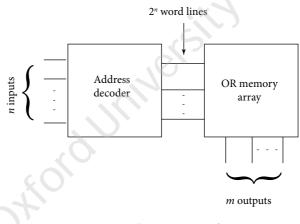

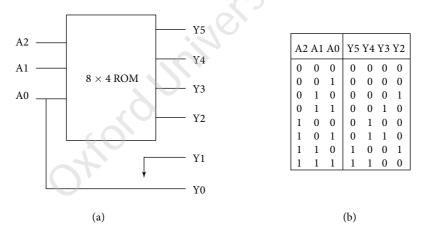

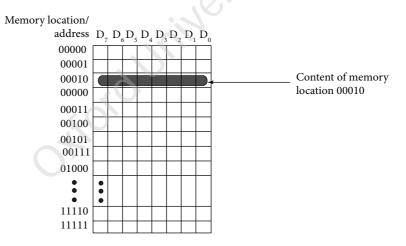

| 1.7  | Memory 65                                                      |   |

|      | 1.7.1 Units of Memory 65                                       |   |

|      | 1.7.2 Architecture of Memory 65                                |   |

|      | 1.7.3 Types of Memories 66                                     |   |

| 1.8  | Control Logic Circuits 66                                      |   |

| 1.9  | e                                                              |   |

|      | 1.9.1 State Diagram vs. ASM Chart 68                           | 2 |

|      | 1.9.2 Realization of ASM Chart 68                              |   |

|      | 1.9.3 Linked State Machine 69                                  |   |

| Intr | oduction to VHDL 77                                            |   |

|      | Introduction 77                                                |   |

|      |                                                                |   |

|      | Historical Background 77                                       | 2 |

| 2.3  | Introduction to VHDL 78                                        |   |

|      | 2.3.1 Entity 78                                                |   |

| 2.4  | 2.3.2 Architecture 79                                          | 2 |

| 2.4  | Basic Language Syntax 79                                       |   |

|      | 2.4.1 Comments 79                                              |   |

|      | 2.4.2 Identifiers 79                                           |   |

| 25   | 2.4.3 Keywords 80                                              | 2 |

| 2.5  | Data Objects 81                                                | 2 |

|      | 2.5.1 Syntax for Data Objects 81                               | 2 |

|      | 2.5.2 Signal Data Objects 81<br>2.5.3 Constant Data Objects 82 | 2 |

|      | 2.5.4 Variable Data Objects 82                                 |   |

|      | 2.5.5 File Data Objects 82                                     |   |

|      | 2.5.6 Other Data Objects 82                                    |   |

| 26   | Data Object Values 83                                          |   |

|      | Data Types 83                                                  |   |

| 2.7  | 2.7.1 Bit and Bit_Vector Types 83                              |   |

|      | 2.7.2 STD_LOGIC and STD_LOGIC_                                 |   |

|      | VECTOR Types 84                                                | 2 |

|      | 2.7.3 STD_ULOGIC Type 84                                       | 2 |

|      | 2.7.4 SIGNED and UNSIGNED Types 84                             |   |

|      | 2.7.5 Integer Type 85                                          |   |

|      | 2.7.6 Boolean Type 85                                          |   |

|      | 2.7.7 Enumeration Type 85                                      |   |

|      | 2.7.8 Floating Point Type 85                                   |   |

|      | 2.7.9 Physical Types 86                                        |   |

|      | 2.7.10 Array Type 86                                           |   |

|      | 2.7.11 File Type 87                                            |   |

|      | 2.7.12 Access Type 87                                          |   |

|      | 2.7.13 Record Type 87                                          |   |

|      | 2.7.14 Subtype 87                                              |   |

|      | <i></i>                                                        |   |

2.

| 2.8  | Operators in VHDL 88                      |

|------|-------------------------------------------|

|      | 2.8.1 Logical Operators 88                |

|      | 2.8.2 Adding Operators 88                 |

|      | 2.8.3 Shift Operators 89                  |

|      | 2.8.4 Relational Operators 90             |

|      | 2.8.5 Multiplying Operators 90            |

|      | 2.8.6 Sign Operators 91                   |

|      | 2.8.7 Miscellaneous Operators 91          |

|      | 2.8.8 Operator Precedence 91              |

| 2.9  | Hardware Modeling 92                      |

|      | 2.9.1 Entity Declaration 92               |

|      | 2.9.2 Architecture Body 93                |

|      | 2.9.3 Configuration Declaration 93        |

|      | 2.9.4 Package Declaration 96              |

|      | 2.9.5 Package Body 96                     |

| 2.10 | Attributes 96                             |

|      | 2.10.1 Predefined Attributes 97           |

|      | 2.10.2 User-defined Attributes 97         |

| 2.11 | Statements in VHDL 97                     |

|      | 2.11.1 Signal Assignment Statements 97    |

|      | 2.11.2 Variable Assignment Statement 97   |

|      | 2.11.3 Wait Statement 98                  |

| 2.12 | Component Declaration 98                  |

|      | Component Instantiation 98                |

|      | Generic Declarations 99                   |

| 2.15 | Concurrent Statements 100                 |

|      | 2.15.1 Concurrent Signal Assignment       |

|      | Statement 100                             |

|      | 2.15.2 Conditional Signal Assignment      |

|      | Statement 100                             |

|      | 2.15.3 Selected Signal Assignment         |

|      | Statement 100                             |

|      | 2.15.4 Block Statement 101                |

|      | 2.15.5 Concurrent Assertion Statement 101 |

| 2.16 | Sequential Statements 101                 |

|      | 2.16.1 Process Statement 101              |

|      | 2.16.2 if Statement 102                   |

|      | 2.16.3 Case Statement 102                 |

|      | 2.16.4 Generate Statement 104             |

|      | 2.16.5 if-generate Statement 106          |

|      | 2.16.6 Select Statement 107               |

|      | 2.16.7 Loop Statement 108                 |

|      | 2.16.8 Exit Statement 109                 |

|      | 2.16.9 Next Statement 109                 |

|      | 2.16.10 Assertion Statement 110           |

|      | 2.16.11 Report Statement 110              |

|      | 2.16.12 NULL Statement 110                |

|    | 2.17 | Library 110                                               |       |    |

|----|------|-----------------------------------------------------------|-------|----|

|    | 2.18 | Package 111                                               |       |    |

|    | 2.19 | Using Library and Package in<br>VHDL 111                  |       |    |

| 3. | Data | aflow Modeling                                            | 114   |    |

|    | 3.1  | Introduction 114                                          |       |    |

|    | 3.2  | Entity Declaration 114                                    |       |    |

|    | 3.3  | Architecture Body 115                                     |       |    |

|    | 3.4  | Concurrent Statement 115                                  |       |    |

|    |      | 3.4.1 Signal Declaration 115                              |       |    |

|    |      | 3.4.2 Signal Assignment Statements                        | 116   |    |

|    | 3.5  | Dataflow Modeling of Basic Logic                          |       |    |

|    |      | Gates 118                                                 |       |    |

|    |      | 3.5.1 Dataflow Model of NOT Gate                          | 118   |    |

|    |      | 3.5.2 Dataflow Model of AND Gate                          | 119   |    |

|    |      | 3.5.3 Dataflow Model of OR Gate 1                         | 19    |    |

|    |      | 3.5.4 Dataflow Model of NAND                              |       |    |

|    |      | Gate 119                                                  |       | 5. |

|    |      | 3.5.5 Dataflow Model of NOR Gate                          | 120   |    |

|    |      |                                                           | 121   |    |

|    |      | 3.5.7 Dataflow Model of XNOR Gate                         | 121   |    |

|    | 3.6  | Datapath Design 121                                       |       |    |

|    |      | 3.6.1 Half-adder using Dataflow Mode<br>Style 122         | ling  |    |

|    |      | 3.6.2 <i>n</i> -bit Adder using Dataflow<br>Modeling 123  |       |    |

|    |      | 3.6.3 Subtractor using Dataflow<br>Modeling 124           |       |    |

|    |      | 3.6.4 Comparator using Dataflow<br>Modeling 127           |       |    |

|    |      |                                                           | 128   |    |

|    |      | 3.6.6 Decoder using Dataflow<br>Modeling 130              |       |    |

|    |      | 3.6.7 Multiplexer using Dataflow<br>Modeling 132          |       |    |

|    |      | 3.6.8 SR Latch using Dataflow<br>Modeling 134             |       |    |

|    |      | 3.6.9 Tri-stated Inverting Buffer using<br>Statement 135  | Block |    |

|    |      | 3.6.10 D Flip-flop using Block                            |       |    |

|    |      | Statement 136                                             |       |    |

|    |      | 3.6.11 Signed Binary Multiplier 137<br>3.6.12 Divider 137 |       | 6. |

| 4. | Beha | avioral Modeling                                          | 141   |    |

| 4.1 Introduction 14 |

|---------------------|

|---------------------|

4.2 Sequential Statements 141

|       | 4.2.1 Process Statement 142                             |

|-------|---------------------------------------------------------|

|       | 4.2.2 Variable Assignment Statement 143                 |

|       | 4.2.3 List of Sequential Statements 143                 |

| 4.3   |                                                         |

|       | D Flip-Flop with Reset Input 145                        |

| 4.5   | •                                                       |

|       | 8-Bit Binary Counter 147                                |

|       | 2:4 Decoder 148                                         |

| 4.8   | 8                                                       |

| 4.0   | 1's in a Stream of Bits 148                             |

|       | Circular Shift Register 150                             |

|       | Serial-in-serial-out Shift Register 152                 |

| 4.11  | Memory 153<br>4.11.1 Read-only Memory 153               |

|       | 4.11.2 Read-write Memory 155                            |

| 4 1 2 | Arithmetic Logic Unit 155                               |

|       | Traffic Light Controller 157                            |

|       |                                                         |

| Stru  | ctural Modeling 161                                     |

| 5.1   | Introduction 161                                        |

| 5.2   | Hierarchy Description 161                               |

|       | 5.2.1 Generics 162                                      |

|       | 5.2.2 Component Declaration 162                         |

|       | 5.2.3 Component Instantiation 163                       |

| 5.0   | 5.2.4 Generate Statement 163                            |

| 5.3   | Full-adder Using Structural Modeling<br>Style 164       |

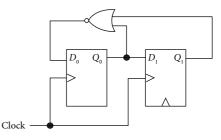

| 5.4   | Serial Adder 166                                        |

| 5.5   | Parallel Adder—Ripple Carry                             |

|       | Adder 168                                               |

|       | Carry Look-ahead Adder 170                              |

|       | Full-subtractor 172                                     |

| 5.8   | Adder or Subtractor Circuit 174                         |

| 5.9   | Unsigned Array Multiplier 176                           |

|       | One or Zero Detector 179                                |

|       | Barrel Shifter 181                                      |

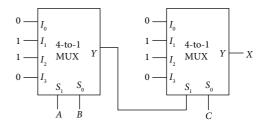

| 5.12  | Design of 16:1 Multiplexer Using 4:1                    |

| E 12  | Multiplexers 183<br>4:16 Decoder Using 2:4 Decoders 186 |

|       | 0                                                       |

| 3.14  | Serial-in-parallel-out 4-bit Shift<br>Register 189      |

| Mixe  | d Modeling 192                                          |

| 6.1   | Introduction 192                                        |

|       | Full-adder 192                                          |

|       | 6.2.1 Alternate Mixed Modeling of Full-                 |

|       | adder 193                                               |

- 6.3 2:4 Decoder with Enable Input 194

- 6.4 T Flip-flop using D Flip-flop 196

- 6.5 Linear Feedback Shift Register 197

- 6.6 Scan Flip-flop 199

#### 7.Concurrent Statements202

- 7.1 Introduction 202

- 7.2 Primary Concurrent Statements 202 7.2.1 Block Statement 202 7.2.2 Process Statement 204

- 7.3 Other Concurrent Statements 205

7.3.1 Concurrent Procedure Call Statement 205

- 7.3.2 Concurrent Signal Assignment Statement 206

- 7.3.3 Concurrent Assertion Statement 207

- 7.3.4 Component Instantiation Statements 209

- 7.3.5 Generate Statement 210

- 8. Sequential Statements 215

- 8.1 Introduction 215

- 8.2 Process Statement 215 8.2.1 Wait Statement 216

- 8.3 Assertion Statement 219

- 8.4 Report Statement 220

- 8.5 Signal Assignment Statement 220 8.5.1 Simple Signal Assignment 220 8.5.2 Conditional Signal Assignment 220

- 8.5.3 Selected Signal Assignment 221

- 8.6 Variable Assignment Statement 221 8.6.1 Simple Variable Assignment 221 8.6.2 Conditional Variable Assignment 221

- 8.6.3 Selected Variable Assignment 221

- 8.7 Procedural Call Statement 222

- 8.8 If Statement 222

- 8.9 Case Statement 223

- 8.10 Loop Statement 224 8.10.1 For Loop 224 8.10.2 While Loop 225

- 8.11 Exit Statement 225

- 8.12 Next Statement 225

- 8.13 Return Statement 226

- 8.14 Null Statement 226

- 9. Advanced VHDL

9.1 Introduction 228

- 9.2 Attributes 228 9.2.1 Predefined Attribute 229 9.2.2 Value Attributes 229 9.2.3 Function Attributes 232 9.2.4 Signal Attributes 235 9.2.5 Type Attribute 238 9.2.6 Range Attributes 239 9.2.7 User-defined Attributes 239 9.3 Group 241 9.4 Configurations 242 9.4.1 Default Binding 242 9.4.2 Configuration Specification 243 9.4.3 Configuration Declaration 247 9.5 Subprograms 252 9.5.1 Functions 252 9.5.2 Nine-valued Resolution 258 9.5.3 Composite-type Resolution 260 9.5.4 Resolved Signal 260

- 9.6 Procedures 261

- 9.7 Subprogram Declaration 262

- 9.8 Subprogram Overloading 264

- 9.9 Operator Overloading 265

- 9.10 Alias Declaration 267

- 9.11 Signatures 267

- 9.12 Guarded Signal 268

- 9.13 Qualified Expression 269

- 10. Arithmetic Logic Unit Design 273

- 10.1 Introduction 273

- 10.2 One Bit ALU 273

- 10.3 Behavioral Design of 16-bit ALU 274

- 10.4 Structural Design of ALU 276

- 10.4.1 Design of Component to Perform Logical Operations 278

- 10.4.2 Design of Component to Perform Arithmetic Operations 282

- 10.4.3 Complement and Transfer Operations Component 286

- 10.4.4 Shift Operations Component 290

- 10.4.5 Design of Control Logic 291

10.4.6 8-bit ALU design 293

11. Model Simulation

- 298

- 11.1 Introduction 298

- 11.2 Testbench 298

- 11.3 Generation of Input Stimulus 299 11.3.1 Clock Waveform Generation 299

228

|     |        | 11.3.2 Non-clock Waveform                                |

|-----|--------|----------------------------------------------------------|

|     |        | Generation 301                                           |

|     |        | 11.3.3 Generation of Waveforms using<br>Vector Table 302 |

|     |        | 11.3.4 Reading Input Vectors From a<br>File 303          |

|     |        | 11.3.5 Writing Results into a File 304                   |

|     | 11.4   | Applying Inputs to the Design Under<br>Test 307          |

|     | 11.5   | Output Checking 308                                      |

|     |        | Types of Testbenches 309                                 |

|     |        | 11.6.1 Example of Stimulus-only                          |

|     |        | Testbench 310                                            |

|     |        | 11.6.2 Example of Full Testbench 311                     |

|     |        | 11.6.3 Hybrid Testbench 314                              |

|     |        | 11.6.4 Fast Testbench 315                                |

|     | 11.7   | File Name as Input 317                                   |

|     | 11.8   | Simulator-specific Testing with                          |

|     |        | ModelSim Simulator 318                                   |

|     | 11.9   | 1 /1                                                     |

|     |        | of Testbenches 319                                       |

|     |        | Event-driven Simulation 319                              |

|     | 11.11  | Cycle-based Simulation 320                               |

| 12. | Delay  | Modeling 322                                             |

|     | 12.1   | Introduction 322                                         |

|     | 12.2   | Delay in Digital Circuits 322                            |

|     | 12.3   | Modeling Wire Delay or Interconnect<br>Delay 323         |

|     | 12.4   | Modeling Inertial Delay 324                              |

|     |        | Default Delay 326                                        |

|     |        | Modeling Gate Delay 327                                  |

|     |        | Gate Delay using Generic Map 328                         |

|     |        | Pin-Specific Delay Modeling 332                          |

|     | 12.9   | Transition-dependent Delay                               |

|     |        | Modeling 333                                             |

|     | 12.10  | Derating of Propagation                                  |

|     |        | Delay depending on Load                                  |

|     |        | Capacitance 334                                          |

|     | 12.11  | Setup and Hold Time Check in D-Flip-<br>Flop 336         |

| 13. | Verifi | cation and Testing 344                                   |

| 15. | 13.1   | •                                                        |

|     | 13.1   |                                                          |

13.2 Verification 344 13.2.1 Simulation 346

- 13.2.2 Formal Verification 346

- 13.2.3 Static Timing Analysis 347

- 13.3 Testing 347 13.3.1 Controllability and Observability 347

- 13.4 Fault Models 348 13.4.1 Equivalent Fault 348

- 13.5 Combinational Logic Testing 348

- 13.6 Sequential Logic Testing 350

13.6.1 Time-frame Expansion Method 351

13.6.2 Simulation-based Method 352

- 13.7 Design for Test 352 13.7.1 Ad Hoc Testing 352

- 13.8 Scan Test 353 13.8.1 Clocked Scan Cell 353 13.8.2 Level-sensitive Scan Design Scan Cell 354

- 13.9 Boundary Scan Test 355

- 13.10 Built-in Self-test 356 13.10.1 Linear Feedback Shift Register 356

- 13.10.2 Signature Analyzer 361

- 13.10.3 Built-in Logic Block Observer 365

- 13.11 Test Generation 366

- 13.11.1 Automatic Test-pattern Generation 366

- 13.11.2 Random Test Generation 366

370

- 13.12 Yield 366

- 14. Synthesis

- 14.1 Introduction 370

- 14.2 Register Transfer Level Synthesis 371

- 14.3 Logic Synthesis 371

- 14.4 Field Programmable Gate Array Synthesis 373

- 14.5 Synthesis of a Combinational Logic using Concurrent Statements 373

- 14.6 Synthesis of a Combinational Logic using Sequential Statements 374

- 14.7 Synthesis of a Sequential Logic using Sequential Statements 375

- 14.8 Synthesis of a D Flip-flop with Asynchronous Reset Using Sequential Statements 377

- 14.9 Synthesis of 4:1 Multiplexer 378

- 14.10 Constraints 379 14.10.1 Timing Constraints 379 14.10.2 Resource Constraints 381 14.11 Synthesizable vs Unsynthesizable Code 382 14.11.1 Purely Combinational Circuits 383 14.11.2 Purely Sequential 383 14.11.3 Purely Synchronous with Asynchronous Set/Reset 384 14.12 Synthesis Examples 385 14.12.1 Full-adder 385 14.12.2 Full-subtractor 386 14.12.3 3:8 Decoder 387 14.12.4 8:1 Multiplexer 389 14.12.5 9-Bit Odd Parity Generator 390 14.12.6 D Flip-flop 391 14.12.7 T Flip-flop 391 14.12.8 MAC Design 392 15. Place and Route 396 15.1 Introduction 396 15.1.1 Translation 397 15.1.2 Mapping 397 15.1.3 Place and Route 397 15.2 Place and Route in FPGA 397 15.3 Placement Algorithm 398 15.3.1 Min-cut Placement Algorithm 398 15.3.2 Greedy Algorithm/Cluster Growth 398 15.3.3 Iterative Simulated Annealing 399 15.3.4 Genetic Algorithm 399 15.4 Routing Algorithm 399 15.4.1 Maze Routing Algorithm 399 15.4.2 PathFinder Algorithm 400 15.4.3 A\* Algorithm 400 15.5 Versatile Place and Route 400 16. File I/O 402 16.1 Introduction 402 16.2 File Declaration 402 16.3 Package TEXTIO 402 16.4 File Opening and Closing 403 16.5 Reading from a File 404 16.6 Writing into a File 404

- 16.7 File Declared in Subprogram 407

|     | 16.8  | File name as Generic or Commar              | nd     |

|-----|-------|---------------------------------------------|--------|

|     | 4 6 0 | Line Argument 408                           |        |

|     | 16.9  | Reading File Name from Standar<br>Input 410 | ď      |

|     | 16.10 | Memory Initialization from a File           | 411    |

| 17. | Float | ing-point Arithmetic                        | 415    |

|     | 17.1  | Introduction 415                            |        |

|     | 17.2  | Real Numbers 415                            |        |

|     |       | 17.2.1 Fractions 415                        |        |

|     |       | 17.2.2 Fixed Point Numbers 416              |        |

|     | 17.3  | Floating-point Number 416                   |        |

|     | 17.4  | 01                                          |        |

|     | 17.5  | Floating-point Multiplication 4             | 22     |

| 18. | Desig | n with FPGA and CPLD                        | 426    |

|     | 18.1  |                                             |        |

|     |       | Programmable Logic Devices 4                | 26     |

|     | 18.3  | Sequential Programmable Logic               |        |

|     | 10.4  | Devices or SPLD 427                         |        |

|     | 18.4  | Complex Programmable Logic D<br>or CPLD 427 | evices |

|     | 18.5  | Xilinx 9500 Series 427                      |        |

|     | 18.6  | Altera Complex Programmable L               | ogic   |

|     |       | Devices Architecture 429                    |        |

|     | 18.7  | Field Programmable Gate Array of FPGA 429   | or     |

|     | 18.8  | Xilinx FPGA 430                             |        |

|     |       | 18.8.1 Xilinx XC2000 FPGA 430               | )      |

|     | 18.9  | 1                                           |        |

|     |       | FPGA Devices 433                            |        |

|     | 18.10 | Design with Xilinx FPGA 433                 |        |

| 19. | Mem   | ories and Buses                             | 437    |

|     | 19.1  |                                             |        |

|     | 19.2  | Memory 437                                  |        |

|     |       | Memory Organization 438                     |        |

|     |       | Read-only Memory 439                        |        |

|     | 19.5  | Random Access Memory 441                    |        |

|     |       | 19.5.1 Static Random Access                 |        |

|     |       | Memory 442                                  |        |

|     |       | 19.5.2 Dynamic Random Access<br>Memory 442  |        |

|     |       | 19.5.3 Memory Array 443                     |        |

|     |       | 19.5.4 Dual-port Random Access              |        |

|     |       | Memory 443                                  |        |

19.6 Bus 446

|       |                | 19.6.1 Bidirectional Bus 446         |

|-------|----------------|--------------------------------------|

|       | 19.7           | Interfacing Memory to Microprocessor |

|       |                | Bus 447                              |

|       |                | 19.7.1 486 Bus Model 449             |

| 20.   | Desig          | n Examples 454                       |

|       | 20.1           | Introduction 454                     |

|       | 20.2           | Multiplier 454                       |

|       |                | 20.2.1 Unsigned Array Multiplier 454 |

|       |                | 20.2.2 Signed Multiplier 457         |

|       |                | 20.2.3 Baugh-Wooley Multiplier 458   |

|       |                | 20.2.4 Booth Multiplier 462          |

|       | 20.3           | Divider 467                          |

|       |                | 20.3.1 Unsigned Divider 468          |

|       |                | Carry Look-Ahead Adder 471           |

|       | 20.5           | First-In First-Out Memory 474        |

|       | 20.6           | State Machines 479                   |

|       |                | 20.6.1 Moore Machine 479             |

|       |                | 20.6.2 Mealy Machine 480             |

|       |                | Case Study: Dice Game 482            |

|       | 20.8           | Microprogramming 483                 |

|       |                | 20.8.1 Microprogramming Example 485  |

|       |                | UART Design 488                      |

|       |                | Microcontroller CPU 495              |

|       |                | Complete Microcontroller 499         |

|       |                | Bus Arbitration 503                  |

|       | 20.13          | Case Study: Vending Machine 503      |

| 21.   | Intro          | duction to Verilog 510               |

|       |                | Introduction 510                     |

|       |                | Basic Verilog Syntax 510             |

|       |                | Some Other Verilog Syntax 511        |

|       | 21.4           | Operators in Verilog 511             |

|       |                | Verilog Data Types 511               |

|       | 21.6           | Numbers in Verilog 512               |

|       |                | 21.6.1 Integer Constants 512         |

|       |                | 21.6.2 Real Constants 512            |

|       |                | Strings 512                          |

|       | 21.8           | Four-Value Logic 512                 |

|       |                | Design with Xilinx FPGA 539          |

|       |                | Lab Exercises 554                    |

|       |                | Mini Projects 565                    |

|       |                | Versions of VHDL: 87 and 93 576      |

|       | ences<br>: 585 | 282                                  |

| inaex | رەر ،          |                                      |

21.9 Behavioral Modeling 513 21.9.1 Behavioral Modeling using Boolean Expression 513 21.9.2 Propagation Delay 513 21.10 Structural Modeling 514 21.11 Delay Modeling in Verilog 515 21.11.1 Inertial Delay 516 21.11.2 Transport Delay 516 21.11.3 Min:Nom:Max Delay Modeling in Verilog 518 21.12 Truth Table Model with Verilog (User-Defined Primitive) 519 21.13 Verilog Statements 519 21.13.1 Assignment Statements 519 21.13.2 Sequential Block 520 21.13.3 Wait Statement 520 21.13.4 Control Statements 521 21.14 Procedures in Verilog 523 21.15 Combinational Logic in Verilog 524 21.16 Sequential Logic in Verilog 524 21.16.1 Modeling of Edge-sensitive Flipflops 524 21.16.2 Blocking and Non-blocking Assignment Statement 525 21.17 Testbenches in Verilog 525 21.18 Example Designs in Verilog 527 21.18.1 Half-adder 527 21.18.2 2:1 Multiplexer with 4-Bit Bus Input 528 21.18.3 D Flip-Flop 528 21.18.4 8-Bit Register 529 21.18.5 4-Bit Counter 529 21.18.6 Clock Generator 530 21.18.7 Seven-segment Display 531 21.18.8 Moore Machine 533 21.18.9 Mealy Machine 534 21.18.10 Hex Keyboard Encoder Circuit 535

# Introduction to Digital Logic Design

#### LEARNING OBJECTIVES

After completing this chapter, the reader will be able to understand the following:

- Boolean algebra

- Basic logic gates

- Combinational logic circuits

- Sequential logic circuits

- Finite state machine

- Memory

- Control logic circuits

- Algorithmic state machine

#### **1.1 INTRODUCTION**

In early ages, human beings used to live in caves, kill animals, and eat raw flesh. With time, they learned how to light fire and make weapons with stones. This age is termed as Stone Age. After the Stone Age, they started learning the use of metals. They made weapons and ornaments with metals, such as Copper and Bronze (alloy of Copper and Tin). This age is termed as Bronze Age. Then they found a harder metal called Iron. The Iron Age was dominated after the Bronze Age. But now it is the Age of Semiconductor. During the nineteenth and twentieth centuries, there has been tremendous growth in electronics and communication technology. It first started with Sir J. C. Bose when he invented first semiconductor detector or Galena detector during the year 1894–1898. Today, we live in the age of modern electronics and communication. We are fully surrounded by electronic gadgets. Starting from the cell phones, camera, watch, toys to personnel computers, all work using the digital technology. Although all practical signals are analog in nature, they are converted to digital because of many advantages of digital technology.

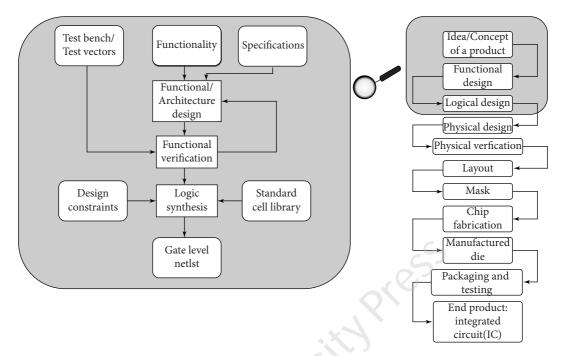

The main purpose of this book is to provide key concepts behind the digital circuit design and learn how to design a complete digital system with the help of formal hardware description language (HDL). Digital circuits are often called logic circuits because of their principle of working is binary in nature. When a large number of such logic circuits are manufactured on a single piece of semiconductor, we get an integrated circuit (IC). The ICs that are used in various electronic gadgets contain huge number of such logic circuits. The technology that is used to manufacture such a large integrated circuit is very-large-scale integration (VLSI) technology. Figure 1.1 illustrates the VLSI design flow where the initial few steps are elaborated in detail.

The very first step is to describe the system from an idea or a concept of end product. This is followed by the architecture or functional design of the system. Then the logic design takes place, which implements the whole big system by using basic logic gates. Once the logical design is finalized, the physical design step starts in which all the circuit components are designed physically and connected by wires within a given chip area. This is followed by the generation of layout of the chip which is nothing but the description of geometrical drawing of the chip. The next step is to generate mask, which can be thought like a negative of photograph. The mask is then taken

FIGURE 1.1 Complete process of making integrated circuit

to the manufacturing unit where wafers are processed to create patterns on them, and the dies are manufactured. The dies are tested and packaged, and the chips are made ready for use. These entire set of steps is very much complex and exhaustive. To know more about the steps, you can refer any text book on VLSI design [Das15]. This paragraph just gives some basic idea about the process of chip design. The important aspect of the diagram is to emphasize the starting step of the design flow. It is required to first describe the behavior of the system using a formal language and therefore we need a language that can describe the behavior of the system efficiently. That is how the concept of a HDL came. VHDL is a formal HDL that is very popular in both academia and industry.

VHDL is used to describe digital logic circuits at different levels of hierarchy starting from very basic gate level up to the system level. The designers can describe the logic circuits in the form of Boolean expressions, or using the behavioral statements that describe the truth table, or using structural description using the components of the design. It can be used for synthesis of the design, timing analysis, and functional verification by doing simulation.

Before we start describing the details of the language, let us first discuss the digital circuits. This course on digital logic circuit design is usually taught in early semester of the undergraduate course. In this chapter, we shall discuss the concepts of digital logic circuit design.

The digital logic circuit works on two states: one state is called a logic high or logic 1 and the other one is called a logic low or logic 0. The logic states can be described by several ways—such as voltage, current, switch mechanical positions, and light on/off state. The logic circuits have finite number of inputs and finite number of outputs. Depending on the inputs, the outputs are either at logic high or at low state. Generally, digital logic circuits are classified into two types: one is called combinational logic and the other one is called sequential logic. In the combinational logic, the outputs are entirely dependent on the present inputs, whereas, in the sequential circuits are memory-less circuits and the sequential circuits have memory.

#### 1.2 BOOLEAN ALGEBRA

Boolean algebra was first introduced by George Boole in 1854. It defines different types of logical operations and works with variables called Boolean variables. The value of the Boolean variables can be either TRUE/HIGH or FALSE/LOW. The digital systems work on binary inputs and produce binary output. In binary system, a TRUE or HIGH state is represented as logic 1 and a FALSE or LOW state is represented as logic 0 in positive logic. In negative logic, a HIGH state is represented by logic 0 and a LOW state is represented by logic 1.

The basic laws of Boolean algebra are shown in Table 1.1.

| TABLE 1.1 | Basic laws of |

|-----------|---------------|

| Boolean   | algebra       |

| A + 0 = A              | $A \cdot 0 = 0$            |

|------------------------|----------------------------|

| A + 1 = 1              | $A \cdot 1 = A$            |

| A + A = A              | $A \cdot A = A$            |

| $A + \overline{A} = 1$ | $A \cdot \overline{A} = 0$ |

#### 1.2.1 Boolean Theorems

Boolean algebra supports three basic laws of simple algebra. These laws are stated as follows:

1. Commutative law:

$$A + B = B + A \tag{1.1}$$

$$A \cdot B = B \cdot A \tag{1.2}$$

2. Associative law:

$$A + (B + C) = (A + B) + C$$

(1.3)

$$A \cdot (B \cdot C) = (A \cdot B) \cdot C \tag{1.4}$$

3. Distributive law:

$$A \cdot (B+C) = A \cdot B + A \cdot C \tag{1.5}$$

$$A + B \cdot C = (A + B) \cdot (A + C) \tag{1.6}$$

DeMorgan's theorems are also very important Boolean theorems, which are extensively used in simplifying the Boolean expressions. These are as follows:

$$\overline{A+B} = \overline{A} \cdot \overline{B} \tag{1.7}$$

$$\overline{A \cdot B} = \overline{A} + \overline{B} \tag{1.8}$$

#### 1.3 BASIC LOGIC GATES

In binary logic, logical operations are used between the binary variables to determine the final output. There are three basic logical operations: NOT, AND, and OR. The electronic circuit that performs the binary operation is called a logic gate.

#### © Oxford University Press. All rights reserved.

4 VHDL: Design, Synthesis, and Simulation

All digital logic circuits are based on three primary logic gates: NOT, AND, and OR gates. Any logic functionality can be achieved by these three primary logic functions. Typically, digital circuits work on the principle of binary logic where there are only two logic values: logic 1 and logic 0. In positive logic, logic 1 is represented by a high-voltage level and logic 0 is represented by a low-voltage level, whereas, in negative logic, logic 1 is represented by a low-voltage level and logic 0 is represented by a high-voltage level. In this book, we shall use positive logic unless stated otherwise.

#### 1.3.1 NOT Gate

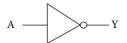

A NOT gate has one input and one output. The symbol of NOT gate is shown in Fig. 1.2.

FIGURE 1.2 Symbol of NOT gate

The output (Y) of NOT gate is the complement of the input (A). The Boolean expression of a NOT gate is described as follows:

$$Y = \overline{A} \tag{1.9}$$

The truth table of NOT gate is shown in Table 1.2.

**TABLE 1.2**Truth table of NOT gate

| A | Y |

|---|---|

| 0 | 1 |

| 1 | 0 |

The NOT gate is also known as inverter.

#### 1.3.2 AND Gate

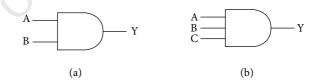

The AND gate has many inputs and one output. The symbols of two-input and three-input AND gates are shown in Fig. 1.3.

FIGURE 1.3 Symbol of AND gate: (a) two-input, (b) three-input

The Boolean expression of the output (Y) for a two-input AND gate is given as follows:

$$Y = A \cdot B \tag{1.10}$$

The truth table of two-input AND gate is shown in Table 1.3.

The AND logic function is associative; that is, any AND function with more than two inputs can be realized using two-input AND functions. For example,

$$Y(A, B, C) = (A \cdot B) \cdot C = A \cdot (B \cdot C) \tag{1.11}$$

© Oxford University Press. All rights reserved.

**TABLE 1.3**Truthtable of AND gate

| Inp | outs | Output |

|-----|------|--------|

| A   | В    | Y      |

| 0   | 0    | 0      |

| 0   | 1    | 0      |

| 1   | 0    | 0      |

| 1   | 1    | 1      |

#### 1.3.3 OR Gate

The OR gate has many inputs and one output. The symbols of two-input and three-input OR gates are shown in Fig. 1.4.

FIGURE 1.4 Symbol of OR gate: (a) two-input, (b) three-input

The Boolean expression of the output (Y) for a two-input OR gate is given as follows:

$$Y = A + B \tag{1.12}$$

The truth table of two-input OR gate is shown in Table 1.4.

| < CO |     |      | <b>.4</b> Truth<br>OR gate |

|------|-----|------|----------------------------|

|      | Inp | outs | Output                     |

|      | Α   | В    | Y                          |

|      | 0   | 0    | 0                          |

|      | 0   | 1    | 1                          |

|      | 1   | 0    | 1                          |

|      | 1   | 1    | 1                          |

The OR logic function is associative; that is, any OR function with more than two inputs can be realized using two-input OR functions. For example,

$$Y(A, B, C) = (A + B) + C = A + (B + C)$$

(1.13)

#### 1.3.4 XOR Gate

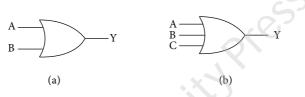

The XOR gate has two or more inputs and one output. The symbols of two-input and three-input XOR gates are shown in Fig. 1.5.

**FIGURE 1.5** Symbol of XOR gate: (a) two-input, (b) three-input

The Boolean expression of the output (Y) for a two-input XOR gate is given as follows:

$$Y = A \oplus B = A\overline{B} + \overline{A}B \tag{1.14}$$

The truth table of two-input XOR gate is shown in Table 1.5.

| Inp | outs | Output |                   |

|-----|------|--------|-------------------|

| Α   | В    | Y      |                   |

| 0   | 0    | 0      | $\langle \rangle$ |

| 0   | 1    | 1      | 1                 |

| 1   | 0    | 1      |                   |

| 1   | 1    | 0      |                   |

|     |      |        | r                 |

**TABLE 1.5**Truthtable of XOR gate

The XOR logic function is associative; that is, any XOR function with more than two inputs can be realized using two-input XOR functions. For example,

$$Y(A, B, C) = (A \oplus B) \oplus C = A \oplus (B \oplus C)$$

(1.15)

#### 1.3.5 NAND Gate

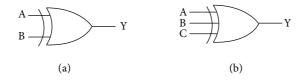

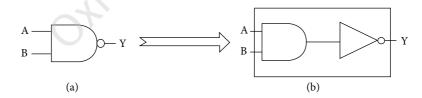

The NAND gate has two inputs and one output. The symbol of NAND gate is shown in Fig. 1.6(a).

FIGURE 1.6 (a) Symbol of NAND gate and (b) its equivalent representation

A NAND gate is equivalent to an AND gate followed by a NOT gate as illustrated in Fig. 1.6(b). The Boolean expression of the output (Y) for a NAND gate is given as follows:

$$Y = \overline{A \cdot B} = \overline{A} + \overline{B} \tag{1.16}$$

The truth table of NAND gate is shown in Table 1.6.

The NAND logic is not associative. The NAND function with more than two inputs cannot be realized using two-input NAND gates.

**TABLE 1.6**Truthtable of NAND gate

| Inp | outs | Output |

|-----|------|--------|

| Α   | В    | Y      |

| 0   | 0    | 1      |

| 0   | 1    | 1      |

| 1   | 0    | 1      |

| 1   | 1    | 0      |

#### 1.3.6 NOR Gate

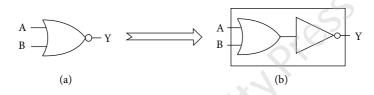

The NOR gate has two inputs and one output. The symbols of NOR gate is shown in Fig. 1.7.

FIGURE 1.7 (a) Symbol of NOR gate and (b) its equivalent representation

A NOR gate is equivalent to an OR gate followed by a NOT gate as illustrated in Fig. 1.7(b). The Boolean expression of the output (Y) for a NOR gate is given as follows:

$$Y = \overline{(A+B)} = \overline{A} \cdot \overline{B} \tag{1.17}$$

The truth table of NOR gate is shown in Table 1.7.

| table of NOR gate |      |        |  |  |  |

|-------------------|------|--------|--|--|--|

| Inp               | outs | Output |  |  |  |

| Α                 | В    | Y      |  |  |  |

| 0                 | 0    | 1      |  |  |  |

| 0                 | 1    | 0      |  |  |  |

| 1                 | 0    | 0      |  |  |  |

| 1                 | 1    | 0      |  |  |  |

TABLE 1.7 Truth

The NOR logic is not associative. The NOR function with more than two inputs cannot be realized using two-input NOR gates.

#### 1.3.7 XNOR Gate

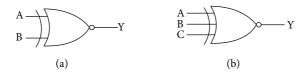

The XNOR gate has two or more inputs and one output. The symbols of two input and three input XNOR gates are shown in Fig. 1.8.

The Boolean expression of the output (Y) for a two-input XNOR gate is given as follows:

$$Y = A \odot B = AB + \overline{A} \overline{B} \tag{1.18}$$

FIGURE 1.8 Symbol of XNOR gate: (a) two-input, (b) three-input

The truth table of two-input XNOR gate is shown in Table 1.8.

**TABLE 1.8**Truthtable of XNOR gate

| Inp | outs | Output |

|-----|------|--------|

| Α   | В    | Y      |

| 0   | 0    | 1      |

| 0   | 1    | 0      |

| 1   | 0    | 0      |

| 1   | 1    | 1      |

The XNOR logic function is associative; that is, any XOR function with more than two inputs can be realized using two-input XOR functions. For example,

$$Y(A, B, C) = (A \odot B) \odot C = A \odot (B \odot C)$$

(1.19)

#### 1.3.8 Universal Gates

The NAND and NOR logic gates are called universal gates because any logic function can be realized using only either NAND or NOR gates.

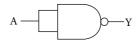

**EXAMPLE 1.1** Realize NOT gate using NAND gate.

#### Solution

The NOT gate can be realized using NAND gate as follows: The NAND gate has two inputs, whereas the NOT gate has single input. If both inputs of NAND gate are shorted together, then the output of NAND gate is as follows:

$$Y = \overline{A \cdot B} = \overline{A \cdot A} = \overline{A} \tag{1.20}$$

Figure 1.9 shows the NOT gate realized using a NAND gate.

FIGURE 1.9 NOT gate realized using NAND gate

**EXAMPLE 1.2** Realize NOT gate using NOR gate.

#### Solution

The NOT gate can be realized using NOR gate as follows: The NOR gate has two inputs, whereas the NOT gate has single input. If both inputs of NOR gate are shorted together, then the output of NOR gate is as follows:

$$Y = \overline{A + B} = \overline{A + A} = \overline{A} \tag{1.21}$$

© Oxford University Press. All rights reserved.

Figure 1.10 shows the NOT gate realized using a NOR gate.

FIGURE 1.10 NOT gate realized using NOR gate

**EXAMPLE 1.3** Realize AND gate using NAND gate.

#### Solution

The AND gate can be realized using NAND gate as shown in Fig. 1.11.

FIGURE 1.11 AND gate realized using NAND gate

**EXAMPLE 1.4** Realize OR gate using NOR gate.

#### Solution

The OR gate can be realized using NOR gate as shown in Fig. 1.12

FIGURE 1.12 OR gate realized using NOR gate

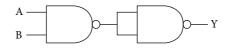

**EXAMPLE 1.5** Realize OR gate using NAND gate.

#### Solution

The OR gate can be realized using NAND as follows: The Boolean expression of NAND gate is given here.

$$F = \overline{A \cdot B} = \overline{A} + \overline{B} \tag{1.22}$$

Now if  $A = \overline{X}$  and  $B = \overline{Y}$ , then it can be written as follows:

$$T = \overline{\overline{X}} + \overline{\overline{Y}} = X + Y$$

(1.23)

Figure 1.13 shows the realization of OR gate using NAND gates.

F

FIGURE 1.13 OR gate realized using NAND gate

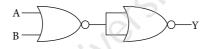

**EXAMPLE 1.6** Realize AND gate using NOR gate.

#### Solution

The AND gate can be realized using NOR gate as follows: The Boolean expression of NOR gate is given here.

$$F = \overline{A + B} = \overline{A} \cdot \overline{B} \tag{1.24}$$

Now, if  $A = \overline{X}$  and  $B = \overline{Y}$ , then it can be written as follows:

$$F = \overline{\overline{X}} \cdot \overline{\overline{Y}} = X \cdot Y \tag{1.25}$$

Figure 1.14 shows the realization of AND gate using NOR gates.

FIGURE 1.14 AND gate realized using NOR gate

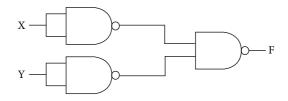

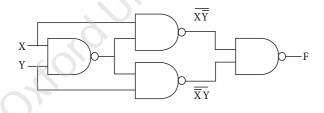

**EXAMPLE 1.7** Realize XOR gate using NAND gate.

#### Solution

The XOR gate can be realized using NAND as follows: The Boolean expression of NAND gate is given here.

$$F = \overline{A \cdot B} = \overline{A} + \overline{B} \tag{1.26}$$

Now, if  $\overline{A} = \overline{X}Y$  and  $\overline{B} = X\overline{Y}$ , then it can be written as follows:

$$F = \overline{X}Y + X\overline{Y} \tag{1.27}$$

Figure 1.15 shows the realization of XOR gate using NAND gates.

FIGURE 1.15 XOR gate realized using NAND gate

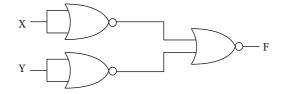

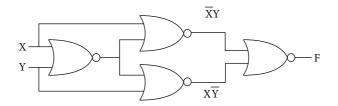

**EXAMPLE 1.8** Realize XNOR gate using NOR gate.

#### Solution

The XNOR gate can be realized using NOR as follows: The Boolean expression of NOR gate is given here.

$$F = \overline{A + B} = \overline{A} \cdot \overline{B} \tag{1.28}$$

Now, if  $\overline{A} = \overline{X}Y$  and  $\overline{B} = X\overline{Y}$ , then it can be written as follows:

$$F = \overline{\overline{X}Y} \cdot \overline{\overline{XY}} = XY + \overline{\overline{X}Y}$$

(1.29)

Figure 1.16 shows the realization of XNOR gate using NOR gates.

FIGURE 1.16 XNOR gate realized using NOR gate

#### 1.3.9 AND-OR-INVERT (AOI) Gate

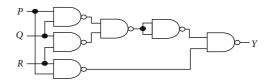

The AOI gate is realized using a combination of AND, OR, and NOT gates. For example, the Boolean expression given in Eq. (1.30) can be realized as shown in Fig. 1.17.

FIGURE 1.17 AND-OR-INVERT gate

$$Y = \overline{AB + CD} \tag{1.30}$$

AOI is useful in realizing any Boolean expression expressed in sum-of-product (SOP) form.

#### 1.3.10 OR-AND-INVERT (OAI) Gate

The OAI gate is realized using a combination of OR, AND, and NOT gates. For example, the Boolean expression given in Eq. (1.31) can be realized as shown in Fig. 1.18.

FIGURE 1.18 OR-AND-INVERT gate

$$Y = \overline{(A+B) \cdot (C+D)} \tag{1.31}$$

OR-AND-INVERT is useful in realizing any Boolean expression expressed in product-of-sum (POS) form.

#### 1.3.11 Buffer Gate

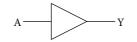

A buffer is a logic gate with one input and one output. The symbol of a buffer is shown in Fig. 1.19.

FIGURE 1.19 Buffer gate

© Oxford University Press. All rights reserved.

It is implemented using two NOT gates connected in cascade. The Boolean expression for the output (Y) is as follows:

$$Y = A \tag{1.32}$$

The truth table of buffer is shown in Table 1.9.

TABLE 1.9 Truth table of buffer gate

| A | Y |

|---|---|

| 0 | 0 |

| 1 | 1 |

A buffer is used in digital circuits to increase the drive capability of a logic gate. For example, let us consider the scenario illustrated in Fig. 1.20. Here, the OR gate is driving four other logic gates.

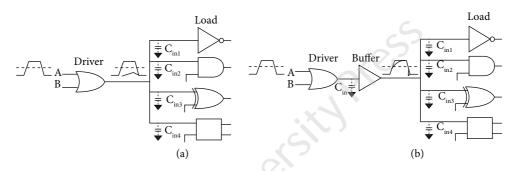

FIGURE 1.20 Driver-load configuration: (a) without a buffer, (b) with a buffer

The effective load capacitance seen by the OR gate is the sum of the input capacitances of four gates. Thus, the total load that the OR gate has to drive is given by  $C_t = C_{in1} + C_{in2} + C_{in3} + C_{in4}$ . This is known as the fan-out of the driver OR gate. If the drive strength of the driver gate is not enough, then the output of the driver will not reach up to the logic high level. This may create logic failure in extreme case when the output of driver is below the logic threshold. This problem can be solved by adding a buffer at the output of the driver. The buffer has less input capacitance ( $C_{in} < < C_t$ ) as compared to  $C_t$  but has large drive strength so that its output will be able to charge the effective load capacitance  $C_t$  up to the logic high level.

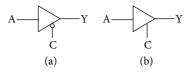

#### 1.3.12 Tri-state Logic Gate

The tri-state logic gate has one data input, one control input, and one output. The control input can be active low or active high. Figure 1.21 shows the symbols of tri-state logic gate with active low and active high control inputs.

FIGURE 1.21 Symbol of tri-state logic gate: (a) active low control input, (b) active high control input

The truth table of tri-state logic gate is shown in Table 1.10. When the active low control input (C) is at logic 0, the buffer is enabled and the output (Y) is same as the input (A). When the active low control input is at logic 1, the buffer is disabled and the output is at high impedance state, which is represented by Z. The high impedance state indicates that the output is neither '1' nor '0', that is, no current flows in this state. The tri-state buffer with active high control input works in opposite way of the tri-state buffer with active low control input.

| Inputs                |   | Output | Output Inputs   |   | Output |

|-----------------------|---|--------|-----------------|---|--------|

| <i>C</i> (active low) | Α | Y      | C (active high) | Α | Y      |

| 0                     | 0 | 1      | 0               | 0 | Ζ      |

| 0                     | 1 | 0      | 0               | 1 | Ζ      |

| 1                     | 0 | Ζ      | 1               | 0 | 0      |

| 1                     | 1 | Ζ      | 1               | 1 | 1      |

**TABLE 1.10**Truth table of tri-state logic gate with active low<br/>and active high inputs

#### 1.3.13 Multi-bit Tri-state Buffer

A multi-bit tri-state buffer has multiple data inputs and outputs but only one control input. In Fig. 1.22, eight tri-state buffers are connected in parallel with common control input. When control is enabled, all eight tri-state buffers transfer their data inputs to their outputs. In the disable state, all the buffer outputs are in high impedance stage.

FIGURE 1.22 Multi-bit tri-state buffer

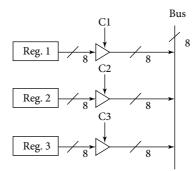

It is used in digital circuits where a bus is driven by multiple logic devices as illustrated in Fig. 1.23.

FIGURE 1.23 Bus architecture with tri-state buffer

In a digital system, it is common that many devices communicate with each other through common bus architecture. Thus, the bus is driven by multiple drivers. However, during the operation, the data on the bus must come from only one device, although there can be multiple devices reading from it. As multiple devices (such as registers) produce output simultaneously and the devices are connected to common bus, there must be a way to control which data gets on the bus, and which does not. The control of data that goes to the bus can be achieved through tri-state buffer. Another possible solution is to use multiplexers, which we shall discuss later in this chapter.

#### 1.3.14 Bus

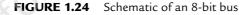

In digital systems, there is a concept of bus architecture. A bus is a group of wires that are used to transmit data from one device to another. For example, in microprocessor architecture, we learned about data bus, address bus, and control bus. The bus size is simply the number of wires in the bus. A bus is schematically drawn by a line with a dash across it. The number beside the dash represents the size of the bus. Figure 1.24 illustrates an 8-bit bus.

The advantage of using bus is that multiple devices can be connected to a bus. Multiple devices can access/read data from the bus simultaneously but they must write into the bus one at a time. There are mainly three kinds of buses: data bus, address bus, and control bus. The data bus is used to read data from the memory or write into the memory. The address bus is used to specify the address of the memory location from which the data is to be read or the address of the memory location to which the data is to be written. Other than data and address buses, there is a control bus, which is used to control the operations in a digital system. One important attribute of bus is its speed. It defines how fast the data can be changed per second. The speed of the bus determines how fast the central processing unit (CPU) can exchange data with the peripheral devices.

#### 1.3.15 Bus Holder Circuit

In bus architecture, it can so happen that multiple devices can simultaneously attempt to write into the bus. This can create erroneous data on the bus and in extreme case may damage the bus wiring. This problem is known as bus contention. The opposite problem of bus contention is bus floating. When no devices drive the bus, the data on the bus is unknown or floating. This floating condition also may damage the logic gates. In order to prevent the bus floating condition, bus holder circuit is used. Bus holder is a weak latch circuit implemented by two NOT gates connected back to back as shown in Fig. 1.25. It holds last value on a tri-state bus and is also known as *bus*

*keeper* circuit. As the bus keeper is made of weak inverters, it can easily be driven to change its output state. It must be noted that although a bus holder works as a latch it must not be used as practical latches.

FIGURE 1.25 Bus holder circuit

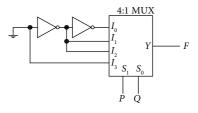

#### 1.3.16 Bidirectional Buffer