# Microelectronic Circuits Theory and Applications

# 7<sup>TH</sup> EDITION South Asia Edition

ADEL S. SEDRA University of Waterloo

KENNETH C. SMITH University of Toronto

Adapted by ARUN N. CHANDORKAR Indian Institute of Technology Bombay

Oxford University Press is a department of the University of Oxford. It furthers the University's objective of excellence in research, scholarship, and education by publishing worldwide. Oxford is a registered trademark of Oxford University Press in the UK and in certain other countries.

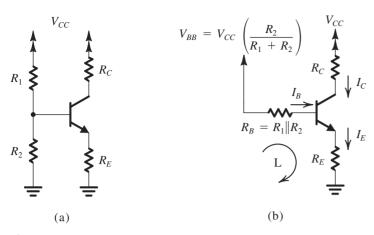

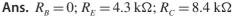

Published in India by Oxford University Press India YMCA Library Building, 1 Jai Singh Road, New Delhi 110001, India

© Oxford University Press India, 2009, 2013, 2017

The moral rights of the author/s have been asserted.

First Indian Edition published in 2009 Second Indian Edition published in 2013 Third Indian Edition published in 2017

Microelectronic Circuits, International Seventh Edition (ISBN: 9780199339143) was originally published in English in 2016 by Oxford University Press USA, 198 Madison Avenue, New York, NY 10016. This adapted edition is published in arrangement with Oxford University Press. Oxford University Press India is solely responsible for this adaptation from the original work. Copyright © 2016 by Oxford University Press

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, without the prior permission in writing of Oxford University Press, or as expressly permitted by law, by licence, or under terms agreed with the appropriate reprographics rights organization. Enquiries concerning reproduction outside the scope of the above should be sent to the Rights Department, Oxford University Press, at the address above.

> You must not circulate this work in any other form and you must impose this same condition on any acquirer.

Multisim and National Instruments are trademarks of National Instruments Corporation. PSpice is a trademark of Cadence Design Systems, Inc. This book is a product of Oxford University Press India, not National Instruments or Cadence Design Systems. Oxford University Press India is solely responsible for the book and its content.

This edition of the text has been adapted and customized for South and South-East Asia. Nor for sale in the USA, Canada, and the UK

> ISBN-13: 978-0-19-947629-9 ISBN-10: 0-19-947629-2

Typeset in Times New Roman by Cameo Corporate Services Limited, Chennai Printed in India by Repro India Ltd, Navi Mumbai

Third-party website addresses mentioned in this book are provided by Oxford University Press in good faith and for information only. Oxford University Press disclaims any responsibility for the material contained therein.

# Preface

This adapted version of *Microelectronic Circuits*, international seventh edition, is intended as a text for the core courses in electronic circuits taught to students pursuing an undergraduate or a postgraduate degree in electrical and electronics engineering. It should also prove useful to engineers and other professionals wishing to update their knowledge through self-study.

As was the case with the first six editions, the objective of this book is to develop in the reader the ability to analyze and design electronic circuits, both analog and digital, discrete and integrated. While the application of integrated circuits is covered, emphasis is placed on transistor circuit design. This is done because of our belief that even if the majority of those studying this book were not to pursue a career in IC design, knowledge of what is inside the IC package would enable intelligent and innovative application of such chips. Furthermore, with the advances in VLSI technology and design methodology, IC design itself has become accessible to an increasing number of engineers.

# Prerequisites

The prerequisite for studying the material in this book is a first course in circuit analysis. As a review, some linear circuits material is included here in the appendices: specifically, two-port network parameters in Appendix C; some useful network theorems in Appendix D; single-time-constant circuits in Appendix E; and *s*-domain analysis in Appendix F. In addition, a number of relevant circuit analysis problems are included at the beginning of the end-of-chapter problems section of Chapter 1. No prior knowledge of physical electronics is assumed. All required semiconductor device physics is included, and Appendix A provides a brief description of IC fabrication. All these appendices can be found on the Oxford University Press India (OUPI)'s website.

# **Emphasis on Design**

It has been our philosophy that circuit design is best taught by pointing out the various tradeoffs available in selecting a circuit configuration and in selecting component values for a given configuration. The emphasis on design has been retained in this edition. In addition to design examples, and designoriented exercises and end-of-chapter problems (indicated with a D), the book includes an extensive appendix (Appendix B on the OUPI website) where a large number of simulation and design examples are presented. These emphasize the use of SPICE, the most valuable circuit-design aid.

# **New to This Edition**

While maintaining the philosophy and pedagogical approach of the first six editions, several changes have been made to both organization and coverage. Our goal in making structural changes has been to

increase modularity and thus flexibility for the instructor, without causing disturbance to courses currently using the sixth edition. Changes in coverage are necessitated by the continuing advances in technology which make some topics of greater relevance and others of less interest. As well, advances in IC process technology require that the numbers used in the examples, exercises and end-of-chapter problems be updated to reflect the parameters of newer generations of IC technologies (e.g., some problems utilize the parameters of the 65-nm CMOS process). This ensures that students are acquiring a real-world perspective on technology.

To improve presentation, a number of chapters and sections have been rewritten for greater clarity. Specific, noteworthy changes are:

- 1. New End-of-Chapter Problems and a New Instructor's Solutions Manual. The number of the end-of-chapter problems has been increased. The new Instructor's Solutions Manual is written by Adel Sedra.

- 2. Expand-Your-Perspective Notes. This is a new feature providing historical and application perspectives. About two such notes are included in each chapter. Most are focused on notable circuit engineers and key inventions.

- **3. Improved Structural Organization.** The content of the book has been restructured by dividing it into four parts. In Part I, Operational Amplifiers (Chapter 2) is discussed before diodes and transistors. This provides readers with opportunity to work and experiment with nontrivial circuits. Part II of the book focuses on analog integrated circuits and Part IV on digital integrated circuits. Part III contains specialized application of the material presented in Parts I and II.

- 4. Greater Flexibility in Presenting the MOSFET and the BJT. Two short and completely parallel chapters present the BJT (Chapter 4) and the MOSFET (Chapter 5). Here the focus is on the device structure and its physical operation, its current–voltage characteristics, and its application in dc circuits. The order of coverage of these two chapters is entirely at the instructor's discretion as they have been written to be completely independent of each other.

- **5.** A Unified Treatment of Transistor Amplifiers. The heart of a first course in electronics is the study of transistor amplifiers. The seventh edition provides a new approach to this subject: A new Chapter 6 begins with the basic principles that underlie the operation of a transistor of either type as an amplifier, and presents such concepts as small-signal operation and modeling. This is followed by the classical configurations of transistor amplifiers, biasing methods, and practical discrete-circuit amplifiers. The combined presentation emphasizes the unity of the basic principles while allowing for separate treatment of the two device types where this is warranted. Very importantly, we are able to compare the two devices and to draw conclusions about their unique areas of application.

- 6. Improved Presentation of Cascoding. Chapter 7 dealing with the basic building blocks of IC amplifiers has been rewritten to improve presentation. Specifically, the development of cascoding and the key circuit building blocks, the cascode amplifier and the cascode current source, is now much clearer.

- **7.** Streamlined Presentation of Frequency Response. In order to keep the treatment of frequency response all together, a new Chapter 9 has been introduced which provides comprehensive coverage of frequency response analysis of amplifiers.

- 8. Clearer and Simplified Study of Feedback. The feedback chapter has been rewritten to improve, simplify and clarify the presentation of this key subject.

- **9.** Updated Treatment of Output Stages and Power Amplifiers. Here, we have updated the material on MOS power transistors and added a new section on the increasingly important class D switching power amplifier.

- **10.** A More Contemporary Approach to Operational Amplifier Circuits. While maintaining coverage of some of the enduring features and subcircuits of the classical 741 op amp, its total coverage is somewhat reduced to make room for modern IC op-amp design techniques.

- 11. Increased Emphasis on Integrated-Circuit Filters and Oscillators. A section on a popular approach to integrated-circuit filter design, namely, transconductance-C filters, has been added to Chapter 13. To make room for this new material, the subsection on stagger-tuned amplifiers has been removed and placed in Appendix H, on the OUPI website. The cross-coupled LC oscillator, popular in IC design, has been added to Chapter 14. The section on precision diode circuits has been removed but is still made available on the website.

- 12. Better Organized and Modernized Coverage of Digital IC Design. Significant improvements have been made to the brief but comprehensive coverage of digital IC design in Part IV. These include a better motivated study of CMOS logic circuits (Chapter 15) which now begins with logic gate circuits. The material on logic circuit technologies and design methodologies as well as the advanced topic of technology scaling and its implications has been moved to Chapter 16. This modularly structured chapter now deals with a selection of advanced and somewhat specialized topics. Since bipolar is hardly ever used in new digital design, coverage of ECL has been significantly reduced. Similarly, BiCMOS has become somewhat of a specialty topic and its coverage has been correspondingly reduced. Nevertheless, the complete material on both ECL and BiCMOS is now available on the website. Finally, we have added a new section on image sensors to Chapter 17 (Memory Circuits).

- **13.** A Useful and Insightful Comparison of the MOSFET and the BJT. This is now included in Appendix G, available on the website.

- 14. PSpice® Simulations (earlier available on the CD that accompanied the sixth edition). The PSpice solutions have been uploaded on the OUPI website from where these can be accessed easily.

- **15.** Multisim<sup>™</sup> Simulations. The website also provides Multisim solutions to the examples and end -of-chapter problems identified with a SIM icon.

# **Exercises and End-of-Chapter Problems**

Over 475 exercises are integrated throughout the text. The answer to each exercise is given below the exercise so students can check their understanding of the material as they read. Solving these exercises should enable the reader to gauge his or her grasp of the preceding material. In addition, nearly 1400 end-ofchapter problems, 65% of which are new or revised in this edition, are provided. The problems are keyed to the individual chapter sections and their degree of difficulty is indicated by a rating system: difficult problems are marked with an asterisk (\*); more difficult problems with two asterisks (\*\*); and very difficult (and/or time-consuming) problems with three asterisks (\*\*\*). We must admit, however, that this classification is by no means exact. Our rating no doubt depended to some degree on our thinking (and mood!) at the time a particular problem was created. Answers to selected problems are given in Appendix L, so students have a checkpoint to tell if they are working out the problems correctly. Complete solutions for all exercises and problems are included in the *Instructor's Solutions Manual*, which is available from the publisher to those instructors who adopt the book.

As in the previous six editions, many examples are included. The examples, and indeed most of the problems and exercises, are based on real circuits and anticipate the applications encountered in designing real-life circuits. This edition continues the use of numbered solution steps in the figures for many examples, as an attempt to recreate the dynamics of the classroom.

# An Outline for the Reader

Part I, *Devices and Basic Circuits*, includes the most fundamental and essential topics for the study of electronic circuits. At the same time, it constitutes a complete package for a first course on the subject.

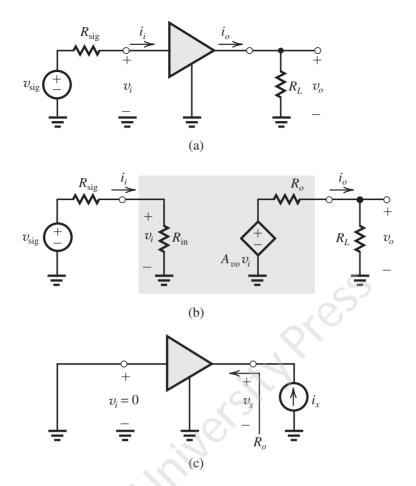

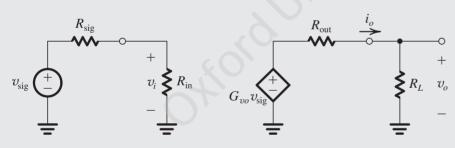

The book starts with an introduction to the basic concepts of electronics in **Chapter 1**. Signals, their frequency spectra, and their analog and digital forms are presented. Amplifiers are introduced as circuit building blocks and their various types and models are studied. This chapter also establishes some of the terminology and conventions used throughout the text.

The second part of the chapter provides an overview of semiconductor concepts at a level sufficient for understanding the operation of diodes and transistors in later chapters. Coverage of this material is useful in particular for students who have had no prior exposure to device physics. Even those with such a background would find a review of this material beneficial as a refresher. The instructor can choose to cover this material in class or assign it for outside reading.

**Chapter 2** deals with operational amplifiers, their terminal characteristics, simple applications, and practical limitations. We chose to discuss the op amp as a circuit building block at this early stage simply because it is easy to deal with and because the student can experiment with op-amp circuits that perform nontrivial tasks with relative ease and with a sense of accomplishment. We have found this approach to be highly motivating to the student. We should point out, however, that part or all of this chapter can be skipped and studied at a later stage (for instance, in conjunction with Chapter 8, Chapter 10, and/or Chapter 12) with no loss of continuity.

The first electronic device, the diode, is studied in **Chapter 3**. The diode terminal characteristics, the circuit models that are used to represent it, and its circuit applications are presented. Depending on the time available in the course, some of the diode applications (e.g. Section 3.6) can be skipped. Also, the brief description of special diode types (Section 3.7) can be left for the student to read.

The foundation of electronic circuits is established by the study of the two transistor types in use today: the bipolar transistor in **Chapter 4** and the MOS transistor in **Chapter 5**. *These two chapters have been written to be completely independent of one another and thus can be studied in either order, as desired.* Furthermore, the two chapters have the same structure, making it easier and faster to study the second device, as well as to draw comparisons between the two device types.

Each of Chapters 4 and 5 begins with a study of the device structure and its physical operation, leading to a description of its terminal characteristics. Then, to allow the student to become very familiar with the operation of the transistor as a circuit element, a large number of examples are presented of dc circuits utilizing the device. The last section of each of Chapters 4 and 5 deals with second-order effects that are included for completeness, but that can be skipped if time does not permit detailed coverage.

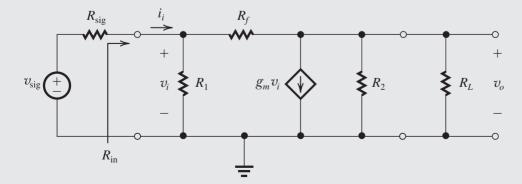

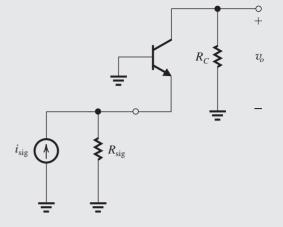

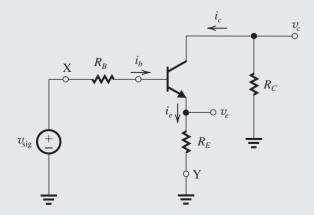

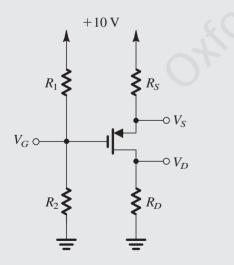

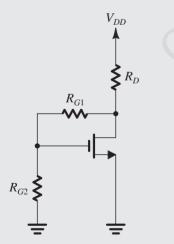

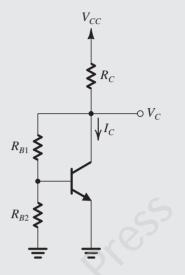

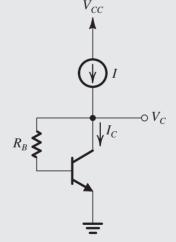

The heart of a first course in electronics is the study of transistor amplifiers. **Chapter 6** (new to this edition) presents a unified treatment of the subject. It begins with the basic principles that underlie the operation of a transistor, of either type, as an amplifier, and proceeds to present the important concepts of small-signal operation and modeling. This is followed by a study of the basic configurations of single-transistor amplifiers. After a presentation of dc biasing methods, the chapter concludes with practical examples of discrete-circuit amplifiers. The combined presentation emphasizes the unity of the basic principles while allowing for separate treatment of the two device types where this is warranted.

Very importantly, we are able to compare the two devices and to draw conclusions about their unique areas of application.

After the study of Part I, the reader will be fully prepared to study either integrated-circuit amplifiers in Part II, or digital integrated circuits in Part IV.

Part II, *Integrated-Circuit Amplifiers*, is devoted to the study of practical amplifier circuits that can be fabricated in the integrated-circuit (IC) form. Its four chapters constitute a coherent treatment of IC amplifier design and can thus serve as the major part of a second course in electronic circuits.

Throughout Part II, both MOS and bipolar circuits are presented side-by-side. Because the MOSFET is by far the dominant device, its circuits are presented first. Bipolar circuits are discussed to the same depth but occasionally more briefly.

Beginning with a brief introduction to the philosophy of IC design, **Chapter 7** presents the basic circuit building blocks that are used in the design of IC amplifiers. These include current mirrors, current sources, gain cells, and cascode amplifiers.

The most important IC building block, the differential pair, is the main topic of **Chapter 8**. The last section of Chapter 8 is devoted to the study of multistage amplifiers.

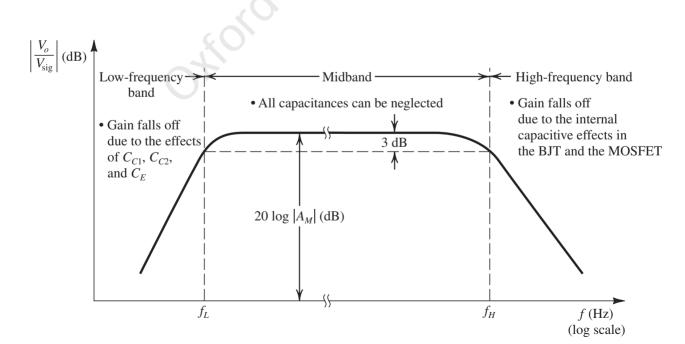

**Chapter 9** (new to this edition) presents a comprehensive treatment of the important subject of amplifier frequency response. Here, Sections 9.1, 9.2, and 9.3 contain essential material; Section 9.4 provides an in-depth treatment of very useful new tools; and Sections 9.5 through 9.8 present the frequency response analysis of a variety of amplifier configurations that can be studied as and when needed. A selection of the latter sections can be made depending on the time available and the instructor's preference.

The fourth of the essential topics of Part II, feedback, is the subject of **Chapter 10**. Both the theory of negative feedback and its application in the design of practical feedback amplifiers are presented. We also discuss the stability problem in feedback amplifiers and treat frequency compensation in some detail.

Part III, *Analog Integrated Circuits*, consists of four chapters, each of which represents a somewhat specialized application of the basic material presented in Parts I and II.

In **Chapter 11** we switch gears from dealing with small-signal amplifiers to those that are required to handle large signals and large amounts of power. Here we study the different amplifier classes—A, B, and AB—and their realization in bipolar and CMOS technologies. We also consider power BJTs and power MOSFETs, and study representative IC power amplifiers. A brief study of the increasingly popular class D amplifier is also presented. Depending on the availability of time, some of the later sections can be skipped in a first reading.

**Chapter 12** brings together all the topics of Chapters 7 through 11 in an important application; namely, the design of operational-amplifier circuits. We study both CMOS and bipolar op amps. In the latter category, besides the classical and still timely 741 circuit, we present modern techniques for the design of low-voltage op amps (Section 12.4).

**Chapter 13** deals with the design of filters, which are important building blocks of communication and instrumentation systems. A comprehensive, design-oriented treatment of the subject is presented. The material provided should allow the reader to perform a complete filter design, starting from specification and ending with a complete circuit realization. A wealth of design tables is included.

**Chapter 14** deals with circuits for the generation of signals with a variety of waveforms: sinusoidal, square, and triangular. We also present circuits for the nonlinear shaping of waveforms.

Part IV, *Digital Integrated Circuits*, provides a brief but nonetheless comprehensive and sufficiently detailed study of digital IC design. Our treatment is almost self-contained, requiring for the most part only a thorough understanding of the MOSFET material presented in Chapter 5. Thus, Part IV can be

studied right after Chapter 5. The only exception to this is the last section in Chapter 16 which requires knowledge of the BJT (Chapter 4). Also, knowledge of the MOSFET internal capacitances (Section 9.2.2) will be needed.

**Chapter 15** is the foundation of Part IV. It begins with the motivating topic of CMOS logic-gate circuits. Then, following a detailed study of digital logic inverters, we concentrate on the CMOS inverter; its static and dynamic characteristics and its design. Transistor sizing and power dissipation round out the topics of Chapter 15. The material covered in this chapter is the minimum needed to learn something meaningful about digital circuits.

**Chapter 16** has a modular structure and presents six topics of somewhat advanced nature. It begins with a presentation of Moore's law and the technology scaling that has made the multi billion-transistor chip possible. This is followed by an overview of digital IC technologies, and the design methodologies that make the design of super-complex digital ICs feasible. Four different logic-circuit types are then presented. Only the last of these includes bipolar transistors.

Digital circuits can be broadly divided into logic and memory circuits. Chapter 17 deals with the latter.

**Appendices**. The twelve appendices contain much useful background and supplementary material. We wish to draw the reader's attention in particular to the first two: Appendix A provides a concise introduction to the important topic of IC fabrication technology including IC layout. Appendix B provides SPICE device models as well as a large number of design and simulation examples in PSpice® and Multisim<sup>TM</sup>. The examples are keyed to the book chapters. These appendices and a great deal more material on these simulation examples can be found on the OUPI website.

# **Online Resources**

The following resources are available at https://india.oup.com/orcs/9780199476299 to support the faculty and students using this book.

# **For Faculty**

- Instructor's Manual

- · PowerPoint-based Figure Slides

- Simulations in Multisim<sup>™</sup> and PSpice<sup>®</sup>

# **For Students**

- Appendices and Additional Material

- Data Sheets

- Simulations in Multisim<sup>™</sup> and PSpice<sup>®</sup>

Adel S. Sedra Kenneth C. (KC) Smith (Late) Arun N. Chandorkar

# **BRIEF CONTENTS**

Preface iii Acknowledgments ix Detailed Contents xiii

#### PART I DEVICES AND BASIC CIRCUITS 1

1 Electronics and Semiconductors 3

2 Operational Amplifiers 85

3 Diodes 163

4 Bipolar Junction Transistors (BJTs) 225

5 MOS Field-Effect Transistors (MOSFETs) 283

6 Transistor Amplifiers 335

#### PART II INTEGRATED-CIRCUIT AMPLIFIERS 457

7 Building Blocks of Integrated-Circuit Amplifiers 459 8 Differential and Multistage Amplifiers 535 9 Frequency Response 625

10 Feedback 725

#### PART III ANALOG INTEGRATED CIRCUITS 827

11 Output Stages and Power Amplifiers 829

12 Operational-Amplifier Circuits 899

13 Filters and Tuned Amplifiers 979

14 Signal Generators and Waveform-Shaping Circuits 1061

#### PART IV DIGITAL INTEGRATED CIRCUITS 1121

15 CMOS Digital Logic Circuits 1123

16 Advanced Topics in Digital Integrated-Circuit Design 1191

17 Memory Circuits 1251

Appendices A–L

Index IN-1

# DETAILED CONTENTS

Preface iii Acknowledgments ix Brief Contents xi

### PART I DEVICES AND BASIC CIRCUITS

## 1 Electronics and Semiconductors

3

Introduction 4 1.1 Signals 4 1.2 Frequency Spectrum of Signals 7 1.3 Analog and Digital Signals 9 1.4 Amplifiers 12 1.4.1 Signal Amplification 12 1.4.2 Amplifier Circuit Symbol 13 1.4.3 Voltage Gain 13 1.4.4 Power Gain and Current Gain 1.4.5 Expressing Gain in Decibels 15 1.4.6 The Amplifier Power Supplies 15 1.4.7 Amplifier Saturation 17 1.4.8 Symbol Convention 17 1.5 Circuit Models for Amplifiers 19 1.5.1 Voltage Amplifiers 19 1.5.2 Cascaded Amplifiers 21 1.5.3 Other Amplifier Types 23 1.5.4 Relationships between the Four Amplifier Models 23 1.5.5 Determining  $R_i$  and  $R_o$  24 1.5.6 Unilateral Models 25 1.6 Frequency Response of Amplifiers 27 1.6.1 Measuring the Amplifier Frequency Response 27 1.6.2 Amplifier Bandwidth 28 1.6.3 Evaluating the Frequency Response of Amplifiers 28 1.6.4 Single-Time-Constant Networks 29

1.6.5 Classification of Amplifiers Based on Frequency Response 35 1.7 Intrinsic Semiconductors 37 1.8 Doped Semiconductors 39 1.9 Current Flow in Semiconductors 42 1.9.1 Drift Current 42 1.9.2 Diffusion Current 45 1.9.3 Relationship between D and  $\mu$  47 1.10 The *pn* Junction 48 1.10.1 Physical Structure 48 1.10.2 Operation with Open-Circuit Terminals 48 1.11 The pn Junction with an Applied Voltage 55 1.11.1 Qualitative Description of Junction Operation 55 1.11.2 The Current–Voltage Relationship of the Junction 57 1.11.3 Reverse Breakdown 62 1.12 Capacitive Effects in the *pn* Junction 63 1.12.1 Depletion or Junction Capacitance 63 1.12.2 Diffusion Capacitance 64

## 2 Operational Amplifiers 85

Introduction 85 2.1 The Ideal Op Amp 86 2.1.1 The Op-Amp Terminals 86

xiii

1

2.1.2 Function and Characteristics of the Ideal Op Amp 87 2.1.3 Differential and Common-Mode Signals 88 2.2 The Inverting Configuration 90 2.2.1 The Closed-Loop Gain 90 2.2.2 Effect of Finite Open-Loop Gain 92 2.2.3 Input and Output Resistances 93 2.2.4 An Important Application—The Weighted Summer 96 2.3 The Noninverting Configuration 98 2.3.1 The Closed-Loop Gain 98 2.3.2 Effect of Finite Open-Loop Gain 99 2.3.3 Input and Output Resistances 100 2.3.4 The Voltage Follower 100 2.4 Difference Amplifiers 102 2.4.1 A Single-Op-Amp Difference Amplifier 102 2.4.2 Controlled Sources 106 2.4.3 A Superior Circuit—The Instrumentation Amplifier 109 2.5 Integrators and Differentiators 113 2.5.1 The Inverting Configuration with General Impedances 113 2.5.2 The Inverting Integrator 115 2.5.3 The Op-Amp Differentiator 120 2.6 DC Imperfections 122 2.6.1 Offset Voltage 122 2.6.2 Input Bias and Offset Currents 125 2.6.3 Effect of  $V_{os}$  and  $I_{os}$  on the Operation of the Inverting Integrator 128 2.7 Effect of Finite Open-Loop Gain and Bandwidth on Circuit Performance 129 2.7.1 Frequency Dependence of the Open-Loop Gain 129 2.7.2 Frequency Response of Closed-Loop Amplifiers 131 2.8 Large-Signal Operation of Op Amps 133 2.8.1 Output Voltage Saturation 133 2.8.2 Output Current Limits 133 2.8.3 Slew Rate 135 2.8.4 Full-Power Bandwidth 136 2.9 Non linear Function Operations 137 2.9.1 Logarithmic Amplifiers 138

2.9.2 Antilogarithmic Amplifiers 1412.9.3 Analog Multipliers 1422.10 Sample and Hold Circuits 143

# 3 Diodes

Introduction 163 3.1 The Ideal Diode 164 3.1.1 Current–Voltage Characteristic 164 3.1.2 A Simple Application: The Rectifier 165 3.1.3 Another Application: Diode Logic Gates 168 3.2 Terminal Characteristics of Junction Diodes 171 3.2.1 The Forward-Bias Region 171 3.2.2 The Reverse-Bias Region 175 3.2.3 The Breakdown Region 176 3.3 Modeling the Diode Forward Characteristic 176 3.3.1 The Exponential Model 176 3.3.2 Graphical Analysis Using the Exponential Model 177 3.3.3 Iterative Analysis Using the Exponential Model 177 3.3.4 The Need for Rapid Analysis 178 3.3.5 The Constant-Voltage-Drop Model 178 3.3.6 The Ideal-Diode Model 179 3.3.7 The Small-Signal Model 180 3.3.8 Use of the Diode Forward Drop in Voltage Regulation 184 3.4 Operation in the Reverse Breakdown Region—Zener Diodes 186 3.4.1 Specifying and Modeling the Zener Diode 187 3.4.2 Use of the Zener as a Shunt Regulator 188 3.4.3 Temperature Effects 190 3.4.4 A Final Remark 190 3.5 Rectifier Circuits 190 3.5.1 The Half-Wave Rectifier 191 3.5.2 The Full-Wave Rectifier 193

163

283

3.5.3 The Bridge Rectifier 194 3.5.4 The Rectifier with a Filter Capacitor—The Peak Rectifier 196 3.5.5 Precision Half-Wave Rectifier—The Superdiode 201 3.6 Limiting and Clamping Circuits 202 3.6.1 Limiter Circuits 202 3.6.2 The Clamped Capacitor or DC Restorer 205 3.6.3 The Voltage Doubler 206 3.7 Special Diode Types 207 3.7.1 The Schottky-Barrier Diode (SBD) 207 3.7.2 Varactors 208 3.7.3 Photodiodes 208 3.7.4 Light-Emitting Diodes (LEDs) 209

# 4 Bipolar Junction Transistors (BJTs)

Introduction 225

- 4.1 Device Structure and Physical Operation 226

- 4.1.1 Simplified Structure and Modes of Operation 226

- 4.1.2 Operation of the *npn* Transistor in the Active Mode 227

225

- 4.1.3 Structure of Actual Transistors 234

- 4.1.4 Operation in the Saturation Mode 235 4.1.5 The *pnp* Transistor 237

- 4.2 Current–Voltage Characteristics 239

- 4.2.1 Circuit Symbols and Conventions 239

- 4.2.2 Graphical Representation of Transistor Characteristics 243

- 4.2.3 Dependence of  $i_c$  on the Collector Voltage—The Early Effect 244

- 4.2.4 An Alternative Form of the Common-Emitter Characteristics 247

- 4.3 BJT Circuits at DC 251

- 4.4 Transistor Breakdown and Temperature Effects 267

- 4.4.1 Transistor Breakdown 267

- 4.4.2 Dependence of  $\beta$  on  $I_c$  and Temperature 269

# 5 MOS Field-Effect Transistors (MOSFETs)

Introduction 283 5.1 Device Structure and Physical Operation 284 5.1.1 Device Structure 284 5.1.2 Operation with Zero Gate Voltage 286 5.1.3 Creating a Channel for Current Flow 286 5.1.4 Applying a Small  $v_{DS}$  288 5.1.5 Operation as  $v_{DS}$  Is Increased 290 5.1.6 Operation for  $v_{DS} \ge V_{OV}$ : **Channel Pinch-Off and Current** Saturation 292 5.1.7 The *p*-Channel MOSFET 295 5.1.8 Complementary MOS or CMOS 296 5.1.9 Operating the MOS Transistor in the Subthreshold Region 297 5.2 Current–Voltage Characteristics 297 5.2.1 Circuit Symbol 297 5.2.2 The  $i_D - v_{DS}$  Characteristics 298 5.2.3 The  $i_D - v_{GS}$  Characteristic 299 5.2.4 Finite Output Resistance in Saturation 303 5.2.5 Characteristics of the *p*-Channel MOSFET 305 5.3 MOSFET Circuits at DC 307 5.4 The Body Effect and Other Topics 317 5.4.1 The Role of the Substrate—The Body Effect 317 5.4.2 Temperature Effects 318 5.4.3 Breakdown and Input Protection 318 5.4.4 Velocity Saturation 319 5.4.5 The Depletion-Type MOSFET 319 5.5 Introduction to MOSFET Scaling 320

# 6 Transistor Amplifiers 335

Introduction 335 6.1 Basic Principles 336 6.1.1 The Basis for Amplifier Operation 336 6.1.2 Obtaining a Voltage Amplifier 337 6.1.3 The Voltage-Transfer Characteristic (VTC) 337

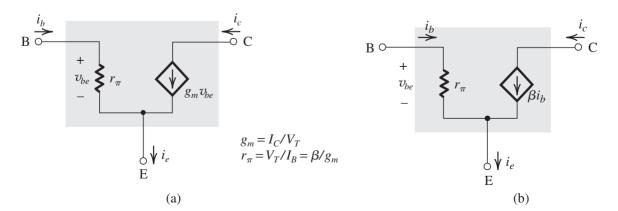

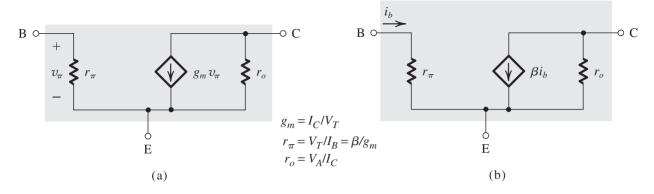

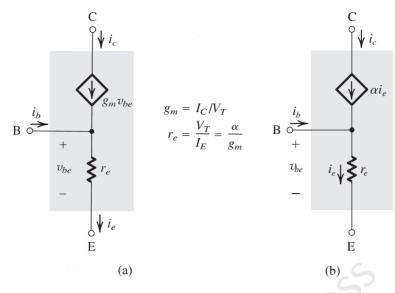

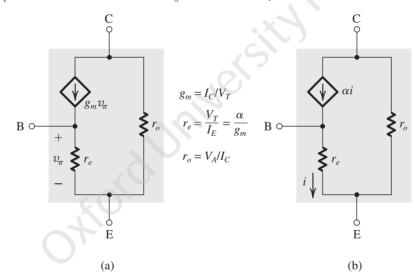

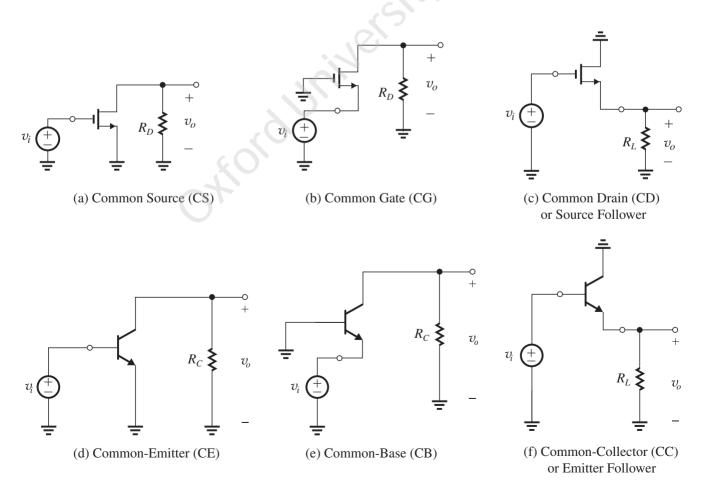

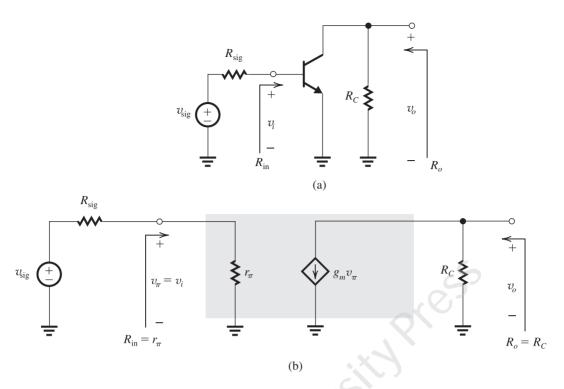

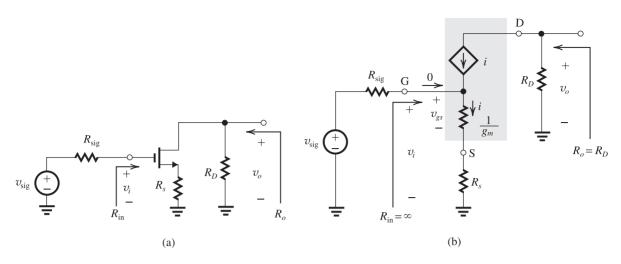

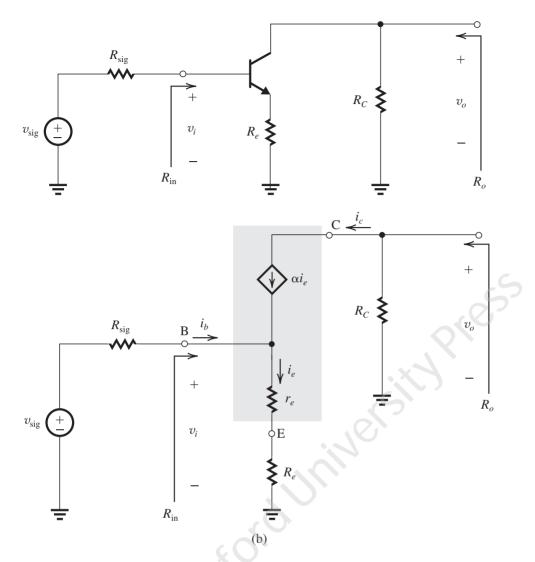

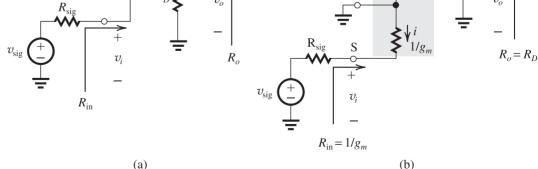

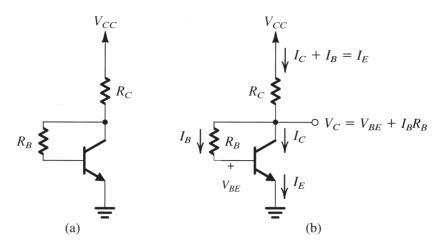

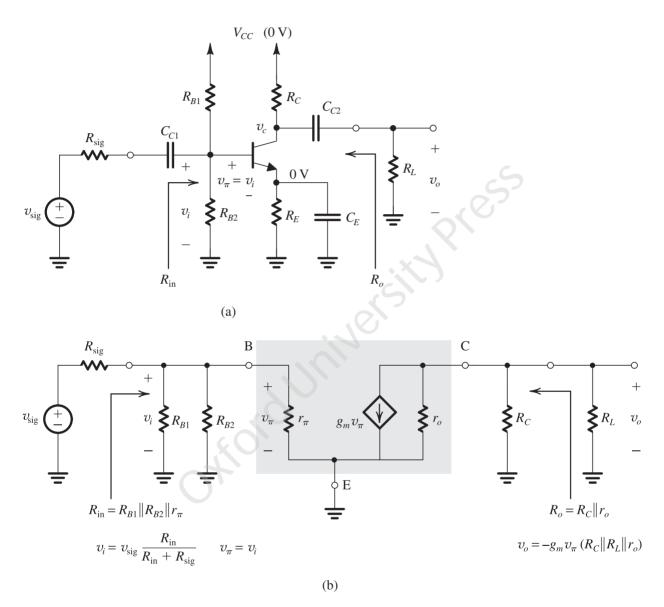

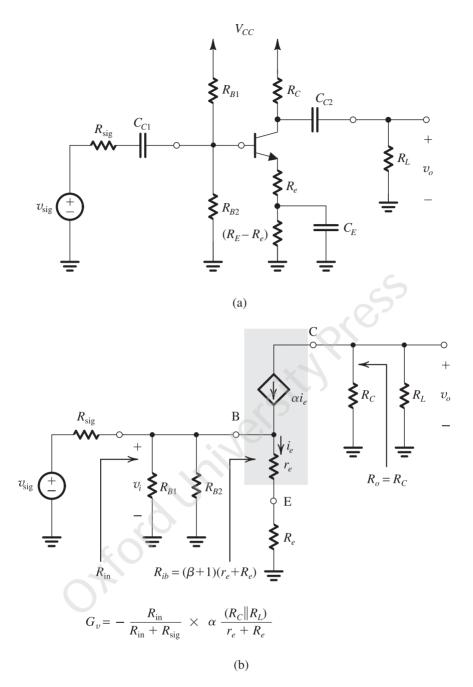

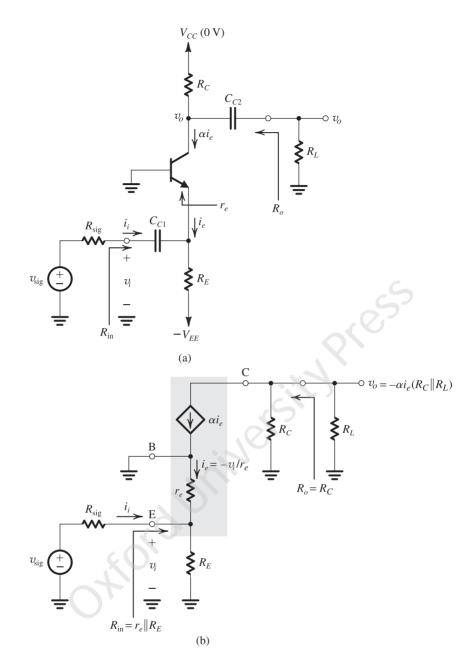

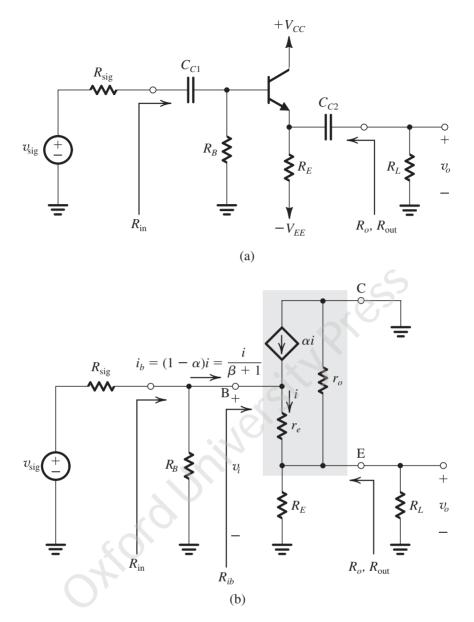

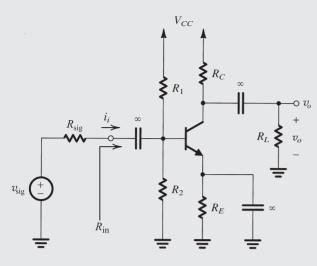

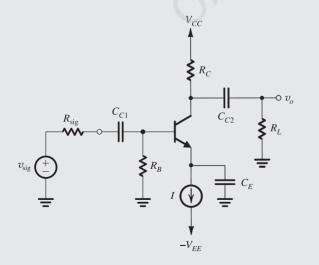

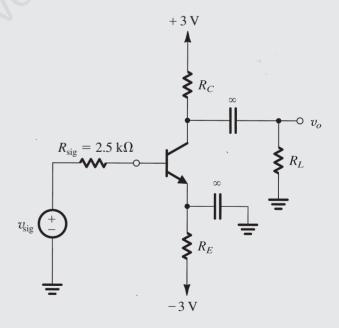

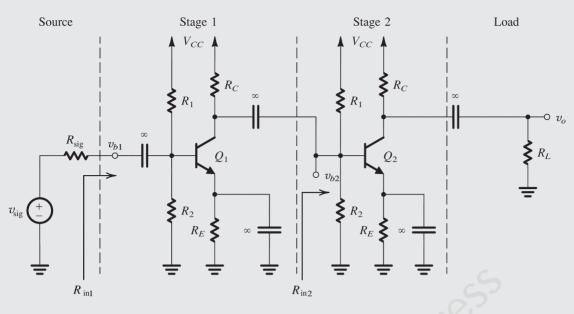

- 6.1.4 Obtaining Linear Amplification by Biasing the Transistor 339 6.1.5 The Small-Signal Voltage Gain 341 6.1.6 Determining the VTC by Graphical Analysis 347 6.1.7 Deciding on a Location for the Bias Point O 348 6.2 Small-Signal Operation and Models 348 6.2.1 The MOSFET Case 349 6.2.2 The BJT Case 362 6.2.3 Summary Tables 379 6.3 Basic Configurations 380 6.3.1 The Three Basic Configurations 382 6.3.2 Characterizing Amplifiers 383 6.3.3 The Common-Source (CS) and Common-Emitter (CE) Amplifiers 385 6.3.4 The Common-Source (Common-Emitter) Amplifier with a Source (Emitter) Resistance 389

- 6.3.5 The Common-Gate (CG) and the Common-Base (CB) Amplifiers 395

- PART II INTEGRATED-CIRCUIT AMPLIFIERS

# 7 Building Blocks of Integrated-Circuit Amplifiers 459

- Introduction 459

- 7.1 IC Design Philosophy 460

- 7.2 IC Biasing—Current Sources, Current Mirrors, and Current-Steering Circuits 461

- 7.2.1 The Basic MOSFET Current Source 462

- 7.2.2 MOS Current-Steering Circuits 464

- 7.2.3 BJT Circuits 466

- 7.2.4 Small-Signal Operation of Current Mirrors 471

- 7.3 The Basic Gain Cell 473

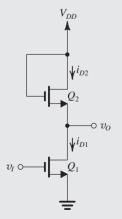

- 7.3.1 The CS and CE Amplifiers with Current-Source Loads 473

- 7.3.2 The Intrinsic Gain 474

- 7.3.3 Effect of the Output Resistance of the Current-Source Load 477

- 7.3.4 Increasing the Gain of the Basic Cell 484

- 6.3.6 The Source and Emitter Followers 399 6.3.7 Summary Tables and Comparisons 407 6.3.8 When and How to Include the Output Resistance  $r_o$  408 6.4 Biasing 409 6.4.1 The MOSFET Case 410 6.4.2 The BJT Case 415 6.5 Discrete-Circuit Amplifiers 420 6.5.1 A Common-Source (CS) Amplifier 421 6.5.2 A Common-Emitter (CE) Amplifier 423 6.5.3 A Common-Emitter Amplifier with an Emitter Resistance  $R_e$  424 6.5.4 A Common-Base (CB) Amplifier 426 6.5.5 An Emitter Follower 427 6.5.6 The Amplifier Frequency Response 429

- 7.4 The Common-Gate and Common-Base Amplifiers 485

7.4.1 The CG Circuit 485

7.4.2 Output Resistance of a CS Amplifier with a Source Resistance 488

7.4.3 The Body Effect 489

7.4.4 The CB Circuit 489

7.4.5 Output Resistance of an Emitter-Degenerated CE Amplifier 491

7.5 The Cascode Amplifier 492

7.5.1 Cascoding 492

7.5.2 The MOS Cascode Amplifier 493

7.5.3 Distribution of Voltage Gain in a Cascode Amplifier 497

457

- 7.5.4 Double Cascoding 499

- 7.5.5 The Folded Cascode 500

- 7.5.6 The BJT Cascode 500

- 7.6 Current-Mirror Circuits with Improved Performance 502

- 7.6.1 Cascode MOS Mirrors 502

- 7.6.2 The Wilson Current Mirror 503

625

7.6.3 The Wilson MOS Mirror 505

7.6.4 The Widlar Current Source 507

7.7 Some Useful Transistor Pairings 509

7.7.1 The CC-CE, CD-CS, and CD-CE Configurations 509

7.7.2 The Darlington Configuration 512

7.7.3 The CC-CB and CD-CG Configurations 513

# 8 Differential and Multistage Amplifiers

# 535

Introduction 535 8.1 The MOS Differential Pair 536 8.1.1 Operation with a Common-Mode Input Voltage 536 8.1.2 Operation with a Differential Input Voltage 540 8.1.3 Large-Signal Operation 542 8.1.4 Small-Signal Operation 545 8.1.5 The Differential Amplifier with Current-Source Loads 550 8.1.6 Cascode Differential Amplifier 551 8.2 The BJT Differential Pair 552 8.2.1 Basic Operation 552 8.2.2 Input Common-Mode Range 554 8.2.3 Large-Signal Operation 555 8.2.4 Small-Signal Operation 556 8.3 Common-Mode Rejection 564 8.3.1 The MOS Case 564 8.3.2 The BJT Case 570 8.4 DC Offset 573 8.4.1 Input Offset Voltage of the MOS Differential Amplifier 573 8.4.2 Input Offset Voltage of the Bipolar Differential Amplifier 576 8.4.3 Input Bias and Offset Currents of the Bipolar Differential Amplifier 578 8.4.4 A Concluding Remark 579 8.5 The Differential Amplifier with a Current-Mirror Load 579 8.5.1 Differential-to-Single-Ended Conversion 580 8.5.2 The Current-Mirror-Loaded MOS Differential Pair 580 8.5.3 Differential Gain of the Current-Mirror-Loaded MOS Pair 581

8.5.4 The Bipolar Differential Pair with a Current-Mirror Load 585

8.5.5 Common-Mode Gain and CMRR 588

8.6 Multistage Amplifiers 592

8.6.1 A Two-Stage CMOS Op Amp 593

8.6.2 A Bipolar Op Amp 597

# 9 Frequency Response

Introduction 625 9.1 Low-Frequency Response of Discrete-Circuit Common-Source and Common-Emitter Amplifiers 627 9.1.1 The CS Amplifier 627 9.1.2 The Method of Short-Circuit Time Constants 634 9.1.3 The CE Amplifier 634 9.2 Internal Capacitive Effects and the High-Frequency Model of the MOSFET and the BJT 638 9.2.1 The MOSFET 638 9.2.2 The BJT 643 9.3 High-Frequency Response of the CS and CE Amplifiers 647 9.3.1 The Common-Source Amplifier 648 9.3.2 The Common-Emitter Amplifier 653 9.3.3 Miller's Theorem 656 9.3.4 Frequency Response of the CS Amplifier When  $R_{sig}$  Is Low 660 9.4 Useful Tools for the Analysis of the High-Frequency Response of Amplifiers 663 9.4.1 The High-Frequency Gain Function 663 9.4.2 Determining the 3-dB Frequency  $f_H$  664 9.4.3 The Method of Open-Circuit Time Constants 666 9.4.4 Application of the Method of Open-Circuit Time Constants to the CS Amplifier 667 9.4.5 Application of the Method of Open-

9.4.5 Application of the Method of Open-Circuit Time Constants to the CE Amplifier 671 9.5 High-Frequency Response of the Common-Gate and Cascode Amplifiers 672 9.5.1 High-Frequency Response of the CG Amplifier 672 9.5.2 High-Frequency Response of the MOS Cascode Amplifier 677 9.5.3 High-Frequency Response of the Bipolar Cascode Amplifier 682 9.6 High-Frequency Response of the Source and Emitter Followers 683 9.6.1 The Source-Follower Case 683 9.6.2 The Emitter-Follower Case 689 9.7 High-Frequency Response of Differential Amplifiers 690 9.7.1 Analysis of the Resistively Loaded MOS Amplifier 690 9.7.2 Analysis of the Current-Mirror-Loaded MOS Amplifier 693 9.8 Other Wideband Amplifier Configurations 698 9.8.1 Obtaining Wideband Amplification by Source and Emitter Degeneration 698 9.8.2 The CD-CS, CC-CE, and CD-CE Configurations 701 9.8.3 The CC-CB and CD-CG

Configurations 705

725

# **10 Feedback**

Introduction 725 10.1 The General Feedback Structure 726 10.1.1 Signal-Flow Diagram 726 10.1.2 The Closed-Loop Gain 727 10.1.3 The Loop Gain 728 10.1.4 Summary 732 10.2 Some Properties of Negative Feedback 732 10.2.1 Gain Desensitivity 732 10.2.2 Bandwidth Extension 733 10.2.3 Interference Reduction 734 10.2.4 Reduction in Nonlinear Distortion 736 10.3 The Feedback Voltage Amplifier 737 10.3.1 The Series-Shunt Feedback Topology 737

10.3.2 Examples of Series-Shunt Feedback Amplifiers 738 10.3.3 Analysis of the Feedback Voltage Amplifier Utilizing the Loop Gain 740 10.3.4 A Final Remark 745 10.4 Systematic Analysis of Feedback Voltage Amplifiers 745 10.4.1 The Ideal Case 745 10.4.2 The Practical Case 747 10.5 Other Feedback-Amplifier Types 756 10.5.1 Basic Principles 756 10.5.2 The Feedback Transconductance Amplifier (Series–Series) 759 10.5.3 The Feedback Transresistance Amplifier (Shunt–Shunt) 770 10.5.4 The Feedback Current Amplifier (Shunt-Series) 778 10.6 Summary of the Feedback Analysis Method 784 10.7 The Stability Problem 784 10.7.1 Transfer Function of the Feedback Amplifier 784 10.7.2 The Nyquist Plot 786 10.8 Effect of Feedback on the Amplifier Poles 787 10.8.1 Stability and Pole Location 788 10.8.2 Poles of the Feedback Amplifier 789 10.8.3 Amplifier with a Single-Pole Response 789 10.8.4 Amplifier with a Two-Pole Response 790 10.8.5 Amplifiers with Three or More Poles 794 10.9 Stability Study Using Bode Plots 796 10.9.1 Gain and Phase Margins 796 10.9.2 Effect of Phase Margin on Closed-Loop Response 796 10.9.3 An Alternative Approach for Investigating Stability 797 10.10 Frequency Compensation 800 10.10.1 Theory 800 10.10.2 Implementation 800 10.10.3 Miller Compensation and Pole Splitting 802

#### PART III ANALOG INTEGRATED CIRCUITS

829

## 11 Output Stages and Power Amplifiers

Introduction 829 11.1 Classification of Output Stages 830 11.2 Class A Output Stage 831 11.2.1 Transfer Characteristic 832 11.2.2 Signal Waveforms 833 11.2.3 Power Dissipation 834 11.2.4 Power-Conversion Efficiency 835 11.2.5 Transformer-Coupled Power Amplifiers 836 11.2.6 Class B Transformer-Coupled Amplifier 838 11.3 Class B Output Stage 840 11.3.1 Circuit Operation 840 11.3.2 Transfer Characteristic 840 11.3.3 Power-Conversion Efficiency 841 11.3.4 Power Dissipation 842 11.3.5 Reducing Crossover Distortion 844 11.3.6 Single-Supply Operation 845 11.4 Class AB Output Stage 845 11.4.1 Circuit Operation 845 11.4.2 Output Resistance 846 11.5 Biasing the Class AB Circuit 849 11.5.1 Biasing Using Diodes 849 11.5.2 Biasing Using the  $V_{BF}$ Multiplier 851 11.6 Variations on the Class AB Configuration 853 11.6.1 Use of Input Emitter Followers 853 11.6.2 Use of Compound Devices 854 11.6.3 Short-Circuit Protection 856 11.6.4 Thermal Shutdown 857 11.7 CMOS Class AB Output Stages 857 11.7.1 The Classical Configuration 857 11.7.2 An Alternative Circuit Utilizing Common-Source Transistors 859 11.8 Class C Output Stage 866 11.8.1 Efficiency of Class C Amplifier 867

11.9 IC Power Amplifiers 868

11.9.1 A Fixed-Gain IC Power Amplifier 869

11.9.2 The Bridge Amplifier 872

11.10 Class D Power Amplifiers 873

11.11 Class S Output Stage 877

11.12 Power Transistors 877

11.12.1 Packages and Heat Sinks 877

11.12.2 Power BJTs 878

11.12.3 Power MOSFETs 880

11.12.4 Thermal Considerations 882

## 12 Operational-Amplifier Circuits

899

Introduction 899 12.1 The Two-Stage CMOS Op Amp 900 12.1.1 The Circuit 900 12.1.2 Input Common-Mode Range and Output Swing 901 12.1.3 DC Voltage Gain 901 12.1.4 Common-Mode Rejection Ratio (CMRR) 905 12.1.5 Frequency Response 905 12.1.6 Slew Rate 909 12.1.7 Power-Supply Rejection Ratio (PSRR) 910 12.1.8 Design Trade-Offs 911 12.1.9 A Bias Circuit for the Two-Stage CMOS Op Amp 912 12.2 The Folded-Cascode CMOS Op Amp 918 12.2.1 The Circuit 918 12.2.2 Input Common-Mode Range and Output Swing 920 12.2.3 Voltage Gain 921 12.2.4 Frequency Response 922 12.2.5 Slew Rate 923 12.2.6 Increasing the Input Common-Mode Range: Rail-to-Rail Input Operation 925

827

12.2.7 Increasing the Output Voltage Range: The Wide-Swing Current Mirror 927 12.3 The 741 BJT Op Amp 928 12.3.1 The 741 Circuit 928 12.3.2 DC Analysis 932 12.3.3 Small-Signal Analysis 937 12.3.4 Frequency Response 949 12.3.5 Slew Rate 951 12.4 Modern Techniques for the Design of BJT Op Amps 952 12.4.1 Special Performance Requirements 952 12.4.2 Bias Design 953 12.4.3 Design of the Input Stage to Obtain Rail-to-Rail V<sub>ICM</sub> 955 12.4.4 Common-Mode Feedback to Control the DC Voltage at the Output of the Input Stage 960 12.4.5 Output-Stage Design for Near Rail-to-Rail Output Swing 964 12.4.6 Concluding Remark 968

# 13 Filters and Tuned Amplifiers

979

Introduction 980 13.1 Filter Transmission, Types, and Specification 980 13.1.1 Filter Transmission 980 13.1.2 Filter Types 981 13.1.3 Filter Specification 982 13.2 The Filter Transfer Function 984 13.3 Butterworth and Chebyshev Filters 987 13.3.1 The Butterworth Filter 987 13.3.2 The Chebyshev Filter 990 13.4 First-Order and Second-Order Filter Functions 994 13.4.1 First-Order Filters 994 13.4.2 Second-Order Filter Functions 997 13.5 The Second-Order LCR Resonator 1002

13.5.1 The Resonator Natural Modes 1002

- 13.5.2 Realization of Transmission Zeros 1003

- 13.5.3 Realization of the Low-Pass Function 1003

- 13.5.4 Realization of the High-Pass Function 1005

- 13.5.5 Realization of the Bandpass Function 1005

- 13.5.6 Realization of the Notch Functions 1005

- 13.5.7 Realization of the All-Pass Function 1006

- 13.6 Second-Order Active Filters Based on Inductor Replacement 1007

- 13.6.1 The Antoniou Inductance-Simulation Circuit 1007

- 13.6.2 The Op Amp–RC Resonator 1009

- 13.6.3 Realization of the Various Filter Types 1010

- 13.6.4 The All-Pass Circuit 1010

- 13.7 Second-Order Active Filters Based on the Two-Integrator-Loop Topology 1015

- 13.7.1 Derivation of the Two-Integrator-Loop Biquad 1015

- 13.7.2 Circuit Implementation 1017

- 13.7.3 An Alternative Two-Integrator-Loop Biquad Circuit 1019

- 13.7.4 Final Remarks 1020

- 13.8 Single-Amplifier Biquadratic Active Filters 1021

- 13.8.1 Synthesis of the Feedback Loop 1021

- 13.8.2 Injecting the Input Signal 1024

- 13.8.3 Generation of Equivalent Feedback Loops 1025

- 13.9 Sensitivity 1029

- 13.10 Transconductance-C Filters 1031

- 13.10.1 Methods for IC Filter Implementation 1032

- 13.10.2 Transconductors 1032

- 13.10.3 Basic Building Blocks 1033

- 13.10.4 Second-Order  $G_m$ -C Filter 1035 13.11 Switched-Capacitor Filters 1038 13.11.1 The Basic Principle 1038 13.11.2 Practical Circuits 1040 13.11.3 Final Remarks 1043 13.12 Tuned Amplifiers 1043 13.12.1 The Basic Principle 1044 13.12.2 Inductor Losses 1045 13.12.3 Use of Transformers 1046 13.12.4 Amplifiers with Multiple Tuned Circuits 1048 13.12.5 The Cascode and the CC-CB Cascade 1049

- 13.12.6 Synchronous Tuning and Stagger Tuning 1050

# 14 Signal Generators and Waveform-Shaping Circuits 1061

Introduction 1061

14.1 Basic Principles of Sinusoidal Oscillators 1062 14.1.1 The Oscillator Feedback Loop 1062 14.1.2 The Oscillation Criterion 1063 14.1.3 Analysis of Oscillator Circuits 1064 14.1.4 Nonlinear Amplitude Control 1067 14.1.5 A Popular Limiter Circuit for Amplitude Control 1068 1069 14.2 Op Amp-RC Oscillator Circuits 14.2.1 The Wien-Bridge Oscillator 1070 14.2.2 The Phase-Shift Oscillator 1073 14.2.3 The Quadrature Oscillator 1079 14.2.4 The Active-Filter-Tuned Oscillator 1081 14.2.5 A Final Remark 1082 14.3 LC and Crystal Oscillators 1082 14.3.1 The Colpitts and Hartley Oscillators 1083

14.3.2 The Cross-Coupled LC Oscillator 1087 14.3.3 Crystal Oscillators 1088 14.4 Bistable Multivibrators 1091 14.4.1 The Feedback Loop 1091 14.4.2 Transfer Characteristic of the Bistable Circuit 1092 14.4.3 Triggering the Bistable Circuit 1093 14.4.4 The Bistable Circuit as a Memory Element 1094 14.4.5 A Bistable Circuit with Noninverting Transfer Characteristic 1094 14.4.6 Application of the Bistable Circuit as a Comparator 1095 14.4.7 Making the Output Levels More Precise 1096 14.5 Generation of Square and Triangular Waveforms Using Astable Multivibrators 1097 14.5.1 Operation of the Astable Multivibrator 1098 14.5.2 Generation of Triangular Waveforms 1100 14.6 Generation of a Standardized Pulse: The Monostable Multivibrator 1102 14.7 Integrated-Circuit Timers 1104 14.7.1 The 555 Circuit 1104 14.7.2 Implementing a Monostable Multivibrator Using the 555 IC 1104 14.7.3 An Astable Multivibrator Using the 555 IC 1105 14.8 Nonlinear Waveform-Shaping Circuits 1107 14.8.1 The Breakpoint Method 1109 14.8.2 The Nonlinear-Amplification Method 1110

## PART IV DIGITAL INTEGRATED CIRCUITS

### 15 CMOS Digital Logic Circuits

### 1123

Introduction 1123 15.1 CMOS Logic-Gate Circuits 1124 15.1.1 Switch-Level Transistor Model 1124 15.1.2 The CMOS Inverter 1124 15.1.3 General Structure of CMOS Logic 1125 15.1.4 The Two-Input NOR Gate 1128 15.1.5 The Two-Input NAND Gate 1128 15.1.6 A Complex Gate 1128 15.1.7 AOI and OAI gates 1129 15.1.8 Obtaining the PUN from the PDN and Vice Versa 1131 15.1.9 The Exclusive-OR Function 1131 15.1.10 Summary of the Synthesis Method 1131 15.2 Digital Logic Inverters 1133 15.2.1 The Voltage-Transfer Characteristic (VTC) 1133 15.2.2 Noise Margins 1135 15.2.3 The Ideal VTC 1136 15.2.4 Inverter Implementation 1137 15.3 The CMOS Inverter 1146 15.3.1 Circuit Operation 1146 15.3.2 The Voltage-Transfer Characteristic (VTC) 1148 15.3.3 The Situation When  $Q_N$  and  $Q_P$ Are Not Matched 1151 15.4 Dynamic Operation of the CMOS Inverter 1155 15.4.1 Propagation Delay 1155 15.4.2 Determining the Propagation Delay of the CMOS Inverter 1159 15.4.3 Determining the Equivalent Load Capacitance C 1165 15.5 Transistor Sizing 1168 15.5.1 Inverter Sizing 1168 15.5.2 Transistor Sizing in CMOS Logic Gates 1170

15.5.3 Effects of Fan-In and Fan-Out on Propagation Delay 1173

15.5.4 Driving a Large Capacitance 1174

15.6 Power Dissipation 1176

15.6.1 Sources of Power Dissipation 1176

15.6.2 Power–Delay and Energy–Delay Products 1179

# 16 Advanced Topics in Digital Integrated-Circuit Design 1191

Introduction 1192 16.1 Implications of Technology Scaling: Issues in Deep-Submicron Design 1192 16.1.1 Silicon Area 1193 16.1.2 Scaling Implications 1193 16.1.3 Velocity Saturation 1195 16.1.4 Subthreshold Conduction 1199 16.1.5 Temperature, Voltage, and Process Variations 1200 16.1.6 Wiring: The Interconnect 1201 16.2 Digital IC Technologies, Logic-Circuit Families, and Design Methodologies 1201 16.2.1 Digital IC Technologies and Logic-Circuit Families 1202 16.2.2 Styles for Digital System Design 1204 16.2.3 Design Abstraction and Computer Aids 1204 16.3 Pseudo-NMOS Logic Circuits 1205 16.3.1 The Pseudo-NMOS Inverter 1205 16.3.2 Static Characteristics 1206 16.3.3 Derivation of the VTC 1206 16.3.4 Dynamic Operation 1209 16.3.5 Design 1210 16.3.6 Gate Circuits 1210 16.3.7 Concluding Remarks 1210

16.4 Pass-Transistor Logic Circuits 1213 16.4.1 An Essential Design Requirement 1214 16.4.2 Operation with NMOS Transistors as Switches 1215 16.4.3 Restoring the Value of  $V_{OH}$  to V<sub>DD</sub> 1219 16.4.4 The Use of CMOS Transmission Gates as Switches 1219 16.4.5 Examples of Pass-Transistor Logic Circuits 1225 1646 A Final Remark 1226 16.5 Dynamic MOS Logic Circuits 1226 16.5.1 The Basic Principle 1227 16.5.2 Nonideal Effects 1230 16.5.3 Domino CMOS Logic 1233 16.5.4 Concluding Remarks 1234 16.6 Bipolar and BiCMOS Logic Circuits 1234 16.6.1 Emitter-Coupled Logic (ECL) 1235 16.6.2 BiCMOS Digital Circuits 1239

# **17 Memory Circuits**

#### 1251

Introduction 1251 17.1 Latches and Flip-Flops 1252 17.1.1 The Latch 1252 17.1.2 The SR Flip-Flop 1254

# Appendices

- A. VLSI Fabrication Technology (on website) A-1

- B. SPICE Device Models and Design and Simulation Examples Using PSpice<sup>®</sup> and Multisim<sup>™</sup> (on website) B-1

- C. Two-Port Network Parameters (on website) C-1

- **D.** Some Useful Network Theorems (on website) D-1

- E. Single-Time-Constant Circuits (on website) E-1

- **F.** *s*-Domain Analysis: Poles, Zeros, and Bode Plots (on website) F-1

17.1.3 CMOS Implementation of SR Flip-Flops 1255 17.1.4 A Simpler CMOS Implementation of the Clocked SR Flip-Flop 1259 17.1.5 D Flip-Flop Circuits 1259 17.2 Semiconductor Memories: Types and Architectures 1262 17.2.1 Memory-Chip Organization 1262 17.2.2 Memory-Chip Timing 1264 17.3 Random-Access Memory (RAM) Cells 1265 17.3.1 Static Memory (SRAM) Cell 1265 17.3.2 Dynamic Memory (DRAM) Cell 1270 17.4 Sense Amplifiers and Address Decoders 1273 17.4.1 The Sense Amplifier 1273 17.4.2 The Row-Address Decoder 1280 17.4.3 The Column-Address Decoder 1282 17.4.4 Pulse-Generation Circuits 1283 17.5 Read-Only Memory (ROM) 1285 17.5.1 A MOS ROM 1285 17.5.2 Mask Programmable ROMs 1287 17.5.3 Programmable ROMs (PROMs,

- EPROMs, and Flash) 1288

- 17.6 CMOS Image Sensors 1290

- **G.** Comparison of the MOSFET and the BJT (on website, also Table G.3 in text) G-1

- H. Design of Stagger-Tuned Amplifiers (on website) H-1

- I. Bibliography (on website) I-1

- J. Standard Resistance Values and Unit Prefixes J-1

- **K.** Typical Parameter Values for IC Devices Fabricated in CMOS and Bipolar Processes K-1

- L. Answers to Selected Problems L-1

- Index IN-1

# **CHAPTER 6**

# **Transistor Amplifiers**

## IN THIS CHAPTER YOU WILL LEARN

- 1. How the transistor (a MOSFET or a BJT) can be used to make an amplifier.

- 2. How to obtain linear amplification from the fundamentally nonlinear MOS and bipolar transistor.

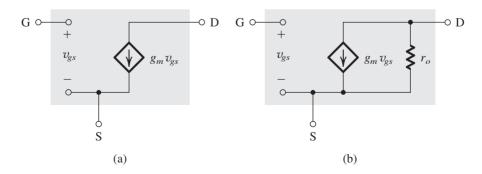

- **3.** How to model the linear operation of a transistor around a bias point by an equivalent circuit that can be used in the analysis and design of transistor amplifiers.

- 4. The three basic ways to connect a MOSFET or a BJT to construct amplifiers with different properties.

- **5.** Practical circuits for MOS and bipolar transistor amplifiers that can be constructed using discrete components.

# Introduction

Having studied the two major transistor types, the BJT (Chapter 4) and the MOSFET (Chapter 5), we now begin the study of their application. There are two distinctly different kinds of transistor application: as a switch, in the design of digital circuits (Chapters 15–17) and as a controlled source, in the design of amplifiers for analog circuits. This chapter and the subsequent six focus on the latter application, namely, the use of the transistor in the design of a variety of amplifier types.

Since the basic principles that underlie the use of the MOSFET and the BJT in amplifier design are the same, the two devices are studied together in this chapter. Besides providing some economy in presentation, this unified study enables us to make important comparisons between MOS and bipolar amplifiers.

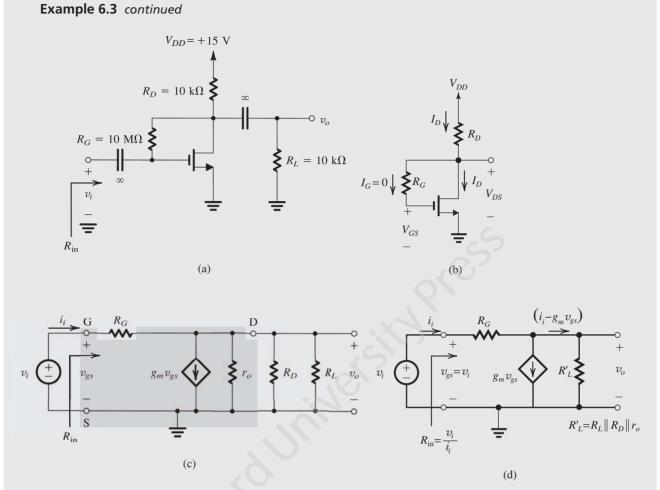

The bulk of this chapter is concerned with the fundamental principles and concepts that are the basis for the application of transistors in amplifier design: We study in detail the models that are used to represent both transistor types in the analysis and design of small-signal linear amplifiers. We also study the three basic configurations in which each of the two transistor types can be connected to realize an amplifier.

The chapter concludes with examples of discrete-circuit amplifiers. These are circuits that can be assembled using discrete transistors, resistors, and capacitors on printed-circuit boards (PCBs). They predominantly use BJTs, and their design differs in significant ways from the design of integrated-circuit (IC) amplifiers. The latter predominantly use MOSFETs, and their study begins in Chapter 7. However, the

fundamental principles and concepts introduced in this chapter apply equally well to both discrete and integrated amplifiers.

# 6.1 Basic Principles

## 6.1.1 The Basis for Amplifier Operation

The basis for the application of the transistor (a MOSFET or a BJT) in amplifier design is that when the device is operated in the active region, a voltage-controlled current source is realized. Specifically, when a MOSFET is operated in the saturation or pinch-off region, also referred to in this chapter as the active region, the voltage between gate and source,  $v_{GS}$ , controls the drain current  $i_D$  according to the square-law relationship which, for an NMOS transistor, is expressed as

$$i_D = \frac{1}{2}k_n(v_{GS} - V_{tn})^2$$

(6.1)

We note that in this first-order model of MOSFET operation, the drain current  $i_D$  does not depend on the drain voltage  $v_{DS}$  because the channel is pinched off at the drain end,<sup>1</sup> thus "isolating" the drain.

Similarly, when a BJT is operated in the active region, the base-emitter voltage  $v_{BE}$  controls the collector current  $i_C$  according to the exponential relationship which, for an *npn* transistor, is expressed as

$$i_C = I_S e^{v_{BE}/V_T}$$

(6.2)

Here, this first-order model of BJT operation indicates that the collector current  $i_c$  does not depend on the collector voltage  $v_{ce}$  because the collector–base junction is reverse biased, thus "isolating" the collector.

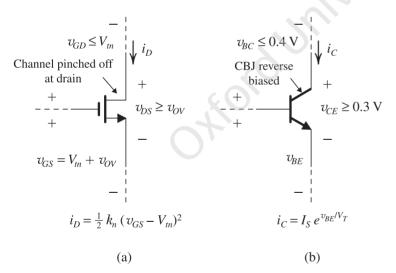

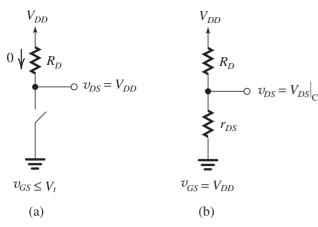

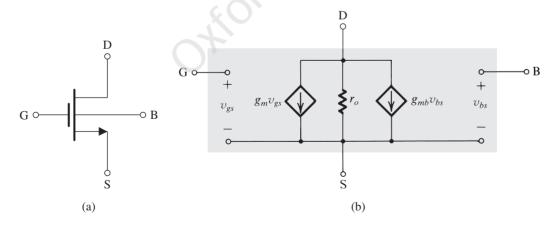

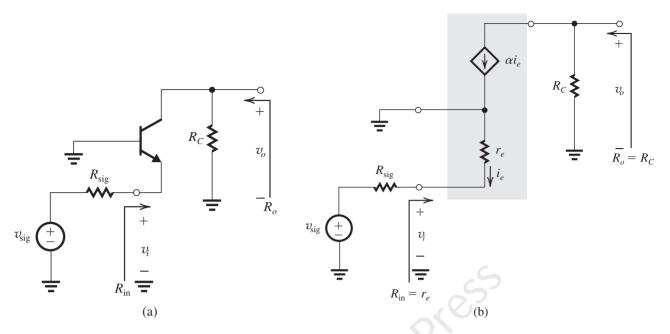

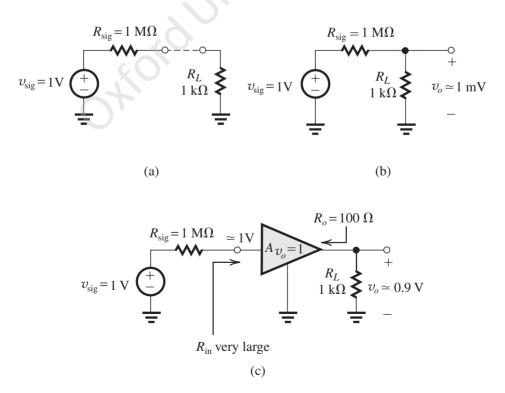

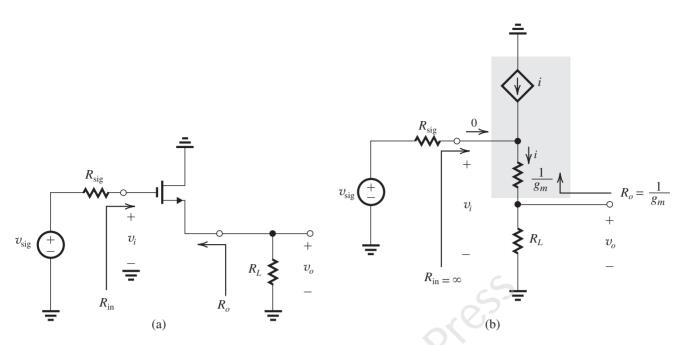

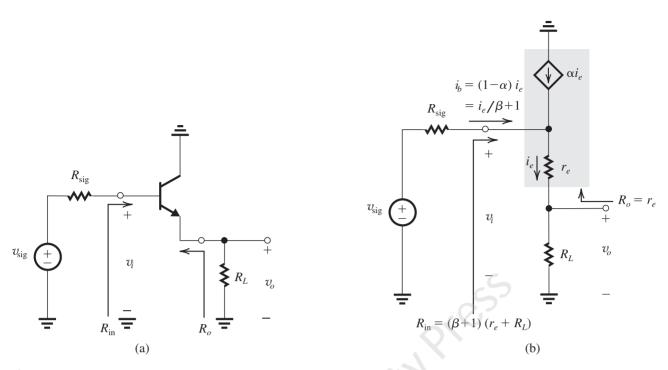

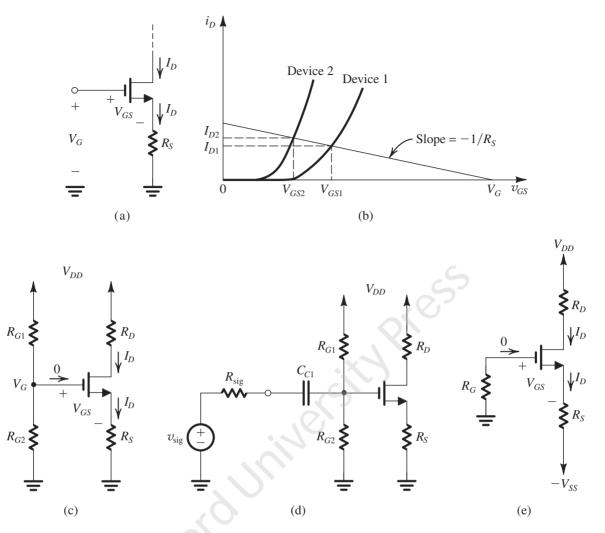

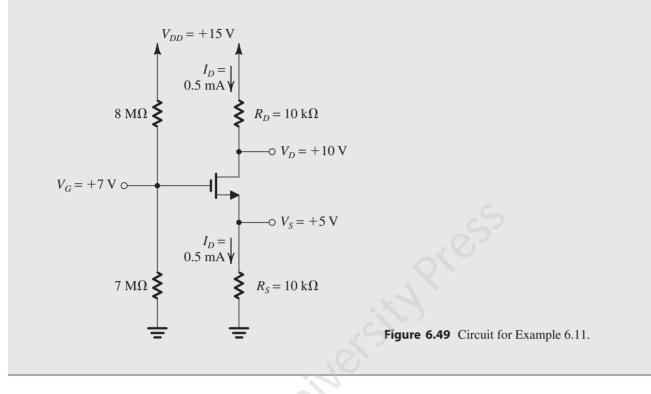

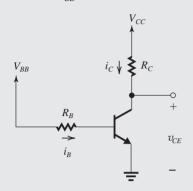

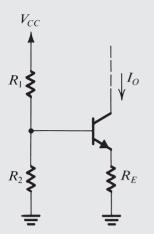

**Figure 6.1** Operating (a) an NMOS transistor and (b) an *npn* transistor in the active mode. Note that  $v_{GS} = V_m + v_{OV}$  and  $v_{DS} \ge v_{OV}$ ; thus  $v_{GD} \le V_m$ , which ensures channel pinch-off at the drain end. Similarly,  $v_{BE} \simeq 0.7$  V, and  $v_{CE} \ge 0.3$  V results in  $v_{BC} \le 0.4$  V, which is sufficient to keep the CBJ from conducting.

Figure 6.1 shows an NMOS transistor and an *npn* transistor operating in the active mode. Observe that for the NMOS transistor, the pinch-off condition is ensured by keeping  $v_{DS} \ge v_{OV}$ . Since the overdrive voltage  $v_{OV} =$  $v_{GS} - V_{tn}$ , this condition implies that  $v_{GD} \le$  $V_{tn}$ , which indeed ensures channel pinch-off at the drain end.

Similarly, for the *npn* transistor in Fig. 6.1(b), the CBJ reverse-bias condition is ensured by keeping  $v_{CE} \ge 0.3$  V. Since  $v_{BE}$  is usually in the vicinity of 0.7 V,  $v_{BC}$  is thus kept smaller than 0.4 V, which is sufficient to prevent this relatively large-area junction from conducting.

Although we used NMOS and *npn* transistors to illustrate the conditions for activemode operation, similar conditions apply for PMOS and *pnp* transistors, as studied in Chapters 5 and 4, respectively.

Finally, we note that the control relationships in Eqs. (6.1) and (6.2) are nonlinear. Nevertheless, we shall shortly devise a technique for obtaining almost-linear amplification from these fundamentally nonlinear devices.

<sup>&</sup>lt;sup>1</sup>To focus on essentials, we shall neglect the Early effect until a later point.

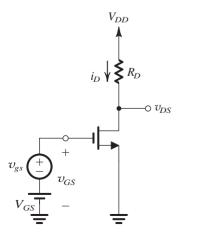

# 6.1.2 Obtaining a Voltage Amplifier

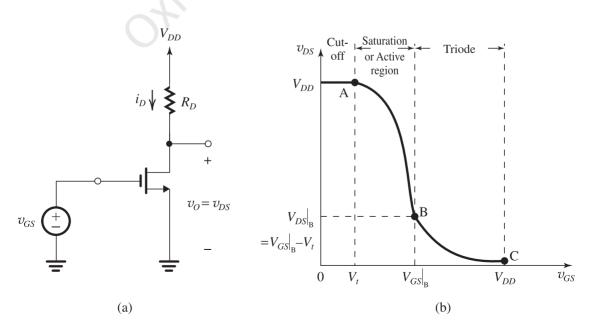

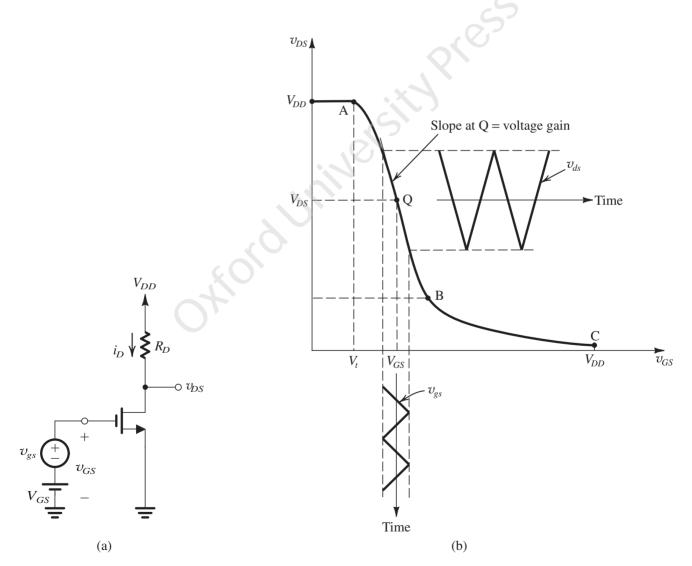

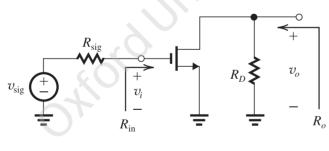

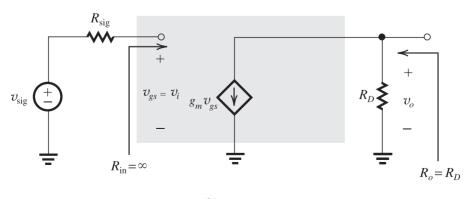

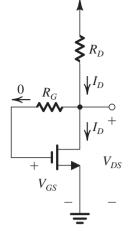

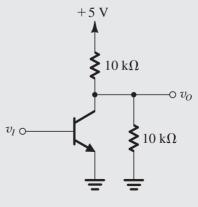

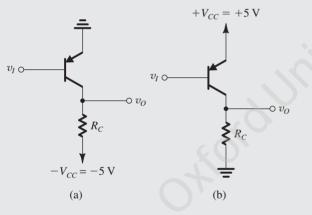

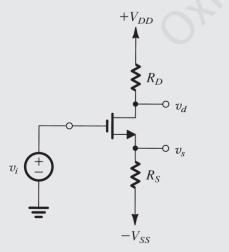

From the above we see that the transistor is basically a transconductance amplifier: that is, an amplifier whose input signal is a voltage and whose output signal is a current. More commonly, however, one is interested in voltage amplifiers. A simple way to convert a transconductance amplifier to a voltage amplifier is to pass the output current through a resistor and take the voltage across the resistor as the output. Doing this for a MOSFET results in the simple amplifier circuit shown in Fig. 6.2(a). Here  $v_{GS}$  is the input voltage,  $R_D$  (known as a **load resistance**) converts the drain current  $i_D$  to a voltage  $(i_D R_D)$ , and  $V_{DD}$  is the supply voltage that powers up the amplifier and, together with  $R_D$ , establishes operation in the active region, as will be shown shortly.

In the amplifier circuit of Fig. 6.2(a) the output voltage is taken between the drain and ground, rather than simply across  $R_D$ . This is done because of the need to maintain a common ground reference between the input and the output. The output voltage  $v_{DS}$  is given by

$$v_{DS} = V_{DD} - i_D R_D \tag{6.3}$$

Thus it is an inverted version (note the minus sign) of  $i_D R_D$  that is shifted by the constant value of the supply voltage  $V_{DD}$ .

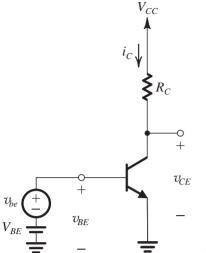

An exactly similar arrangement applies for the BJT amplifier, as illustrated in Fig. 6.2(c). Here the output voltage  $v_{CE}$  is given by

$$v_{CE} = V_{CC} - i_C R_C \tag{6.4}$$

# 6.1.3 The Voltage-Transfer Characteristic (VTC)

A useful tool that provides insight into the operation of an amplifier circuit is its voltage-transfer characteristic (VTC). This is simply a plot (or a clearly labeled sketch) of the output voltage versus the input voltage. For the MOS amplifier in Fig. 6.2(a), this is the plot of  $v_{DS}$  versus  $v_{GS}$  shown in Fig. 6.2(b).

Observe that for  $v_{GS} < V_t$ , the transistor is cut off,  $i_D = 0$  and, from Eq. (6.3),  $v_{DS} = V_{DD}$ . As  $v_{GS}$  exceeds  $V_t$ , the transistor turns on and  $v_{DS}$  decreases. However, since initially  $v_{DS}$  is still high, the MOSFET will be operating in saturation or the active region. This continues as  $v_{GS}$  is increased until the value of  $v_{GS}$  is reached that results in  $v_{DS}$  becoming lower than  $v_{GS}$  by  $V_t$  volts (point B on the VTC in Fig. 6.2b). For  $v_{GS}$  greater than that at point B, the transistor operates in the triode region and  $v_{DS}$  decreases more slowly.

Figure 6.2 (a) An NMOS amplifier and (b) its VTC; and (c) an *npn* amplifier and (d) its VTC.

The VTC in Fig. 6.2(b) indicates that the segment of greatest slope (hence potentially the largest amplifier gain) is that labeled AB, which corresponds to operation in the active region. When a MOSFET is operated as an amplifier, its operating point is confined to the segment AB at all times. An expression for the segment AB can be obtained by substituting for  $i_D$  in Eq. (6.3) by its active-region value from Eq. (6.1), thus

$$v_{DS} = V_{DD} - \frac{1}{2}k_n R_D (v_{GS} - V_t)^2$$

(6.5)

This is obviously a nonlinear relationship. Nevertheless, linear (or almost-linear) amplification can be obtained by using the technique of biasing the MOSFET. Before considering biasing, however, it is useful to determine the coordinates of point B, which is at the boundary between the saturation and the triode regions of operation. These can be obtained by substituting in Eq. (6.5),  $v_{GS} = V_{GS}|_{B}$  and  $v_{DS} = V_{DS}|_{B} = V_{GS}|_{B} - V_{t}$ . The result is

$$V_{GS}|_{\rm B} = V_t + \frac{\sqrt{2k_n R_D V_{DD} + 1} - 1}{k_n R_D}$$

(6.6)

Point B can be alternatively characterized by the overdrive voltage

$$V_{OV}|_{\rm B} \equiv V_{GS}|_{\rm B} - V_t = \frac{\sqrt{2k_n R_D V_{DD} + 1} - 1}{k_n R_D}$$

(6.7)

and

$$V_{DS}\big|_{\mathsf{B}} = V_{OV}\big|_{\mathsf{B}} \tag{6.8}$$

An exactly similar development applies to the BJT case. This is illustrated in Fig. 6.2(c) and (d). In this case, over the active-region or amplifier segment AB, the output voltage  $v_{CE}$  is related to the input voltage  $v_{BE}$  by

$$v_{CE} = V_{CC} - R_C I_S e^{v_{BE}/V_T}$$

(6.9)

Here also, the input–output relationship is nonlinear. Nevertheless, linear (or almost-linear) amplification can be obtained by using the biasing technique discussed next.

#### **EXERCISE**

**6.1** Consider the amplifier of Fig. 6.2(a) with  $V_{DD} = 1.8 \text{ V}$ ,  $R_D = 17.5 \text{ k}\Omega$ , and with a MOSFET specified to have  $V_t = 0.4 \text{ V}$ ,  $k_n = 4 \text{ mA/V}^2$ , and  $\lambda = 0$ . Determine the coordinates of the end points of the active-region segment of the VTC. Also, determine  $V_{DS}|_C$  assuming  $V_{GS}|_C = V_{DD}$ .

**.ns.** A: 0.4 V, 1.8 V; B: 0.613 V, 0.213 V;

$$V_{DS}|_{C} = 18 \text{ mV}$$

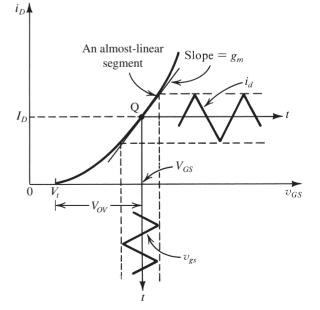

# 6.1.4 Obtaining Linear Amplification by Biasing the Transistor

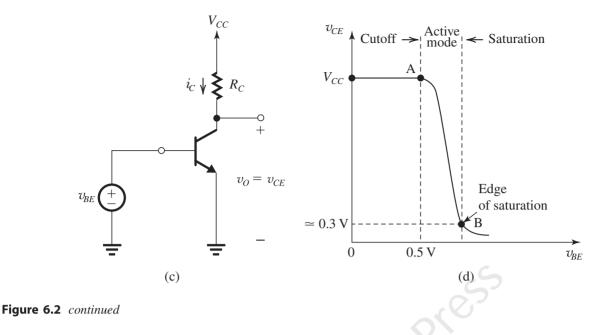

Biasing enables us to obtain almost-linear amplification from the MOSFET and the BJT. The technique is illustrated for the MOSFET case in Fig. 6.3(a). A dc voltage  $V_{GS}$  is selected to obtain operation at a point Q on the segment AB of the VTC. How to select an appropriate location for the bias point Q will be discussed shortly. For the time being, observe that the coordinates of Q are the dc voltages  $V_{GS}$  and  $V_{DS}$ , which are related by

$$V_{DS} = V_{DD} - \frac{1}{2}k_n R_D (V_{GS} - V_t)^2$$

(6.10)

Point Q is known as the **bias point** or the **dc operating point**. Also, since at Q no signal component is present, it is also known as the **quiescent point** (which is the origin of the symbol Q).

Next, the signal to be amplified,  $v_{gs}$ , a function of time *t*, is superimposed on the bias voltage  $V_{GS}$ , as shown in Fig. 6.4(a). Thus the total instantaneous value of  $v_{GS}$  becomes

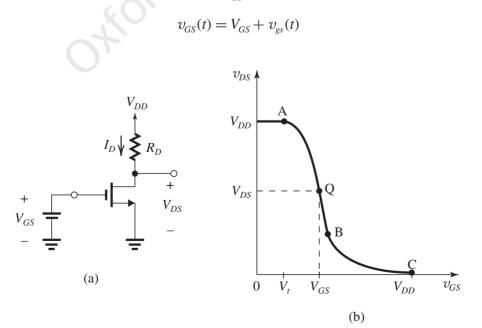

Figure 6.3 Biasing the MOSFET amplifier at a point Q located on the segment AB of the VTC.

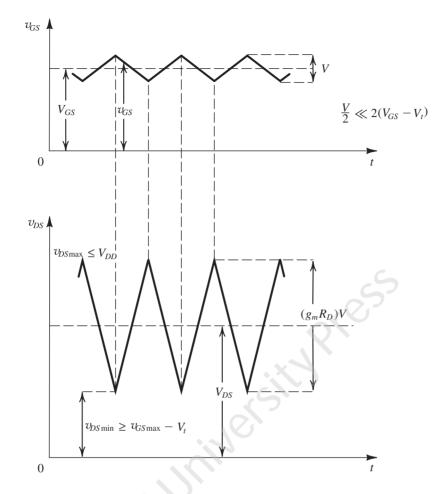

The resulting  $v_{DS}(t)$  can be obtained by substituting for  $v_{GS}(t)$  into Eq. (6.5). Graphically, we can use the VTC to obtain  $v_{DS}(t)$  point by point, as illustrated in Fig. 6.4(b). Here we show the case of  $v_{gs}$  being a triangular wave of "small" amplitude. Specifically, the amplitude of  $v_{gs}$  is small enough to restrict the excursion of the instantaneous operating point to a short, almost-linear segment of the VTC around the bias point Q. The shorter the segment, the greater the linearity achieved, and the closer to an ideal triangular wave the signal component at the output,  $v_{ds}$ , will be. This is the essence of obtaining linear amplification from the nonlinear MOSFET.

Before leaving Fig. 6.4(b) we wish to draw the reader's attention to the consequence of increasing the amplitude of the signal  $v_{gs}$ . As the instantaneous operating point will no longer be confined to the almost-linear segment of the VTC, the output signal  $v_{ds}$  will deviate from its ideal triangular shape; that is, it will exhibit nonlinear distortion. Worse yet, if the input signal amplitude becomes sufficiently large, the instantaneous operating point may leave the segment AB altogether. If this happens at the negative peaks of  $v_{gs}$ , the transistor will cut off for a portion of the cycle and the positive peaks of  $v_{ds}$  will be "clipped off." If it occurs at the positive peaks of  $v_{gs}$ , the transistor will enter the triode region for a

**Figure 6.4** The MOSFET amplifier with a small time-varying signal  $v_{gs}(t)$  superimposed on the dc bias voltage  $V_{GS}$ . The MOSFET operates on a short almost-linear segment of the VTC around the bias point Q and provides an output voltage  $v_{ds} = A_v v_{gs}$ .

portion of the cycle, and the negative peaks of  $v_{ds}$  will become flattened. It follows that the selection of the location of the bias point Q can have a profound effect on the maximum allowable amplitude of  $v_{ds}$ , referred to as the *allowable signal swing at the output*. We will have more to say later on this important point.

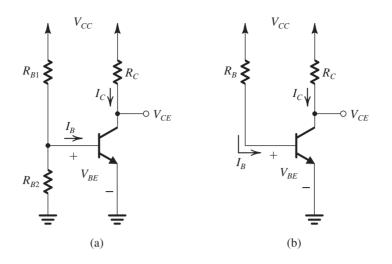

An exactly parallel development can be applied to the BJT amplifier. In fact, all we need to do is replace the NMOS transistor in Figs. 6.3 and 6.4 with an *npn* transistor and change the voltage and current symbols to their BJT counterparts. The resulting bias point Q will be characterized by dc voltages  $V_{BE}$  and  $V_{CE}$ , which are related by

$$V_{CE} = V_{CC} - R_C I_S e^{V_{BE}/V_T}$$

(6.11)

and a dc current  $I_C$ ,

$$I_{C} = I_{S} e^{V_{BE}/V_{T}}$$

(6.12)

Also, superimposing a small-signal  $v_{be}$  on the dc bias voltage  $V_{BE}$  results in

$$v_{BE}(t) = V_{BE} + v_{be}(t)$$

which can be substituted into Eq. (6.9) to obtain the total instantaneous value of the output voltage  $v_{CE}(t)$ . Here again, almost-linear operation is obtained by keeping  $v_{be}$  small enough to restrict the excursion of the instantaneous operating point to a short, almost-linear segment of the VTC around the bias point Q. Similar comments also apply to the maximum allowable signal swing at the output.

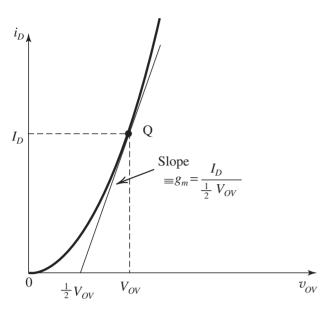

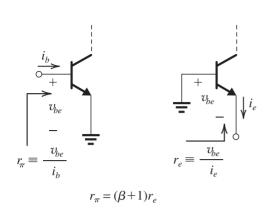

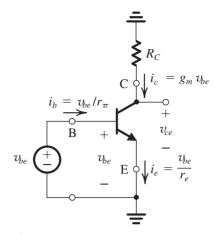

# 6.1.5 The Small-Signal Voltage Gain

**The MOSFET Case** Consider the MOSFET amplifier in Fig. 6.4(a). If the input signal  $v_{gs}$  is kept small, the corresponding signal at the output  $v_{ds}$  will be nearly proportional to  $v_{gs}$  with the constant of proportionality being the slope of the almost-linear segment of the VTC around Q. This is the voltage gain of the amplifier, and its value can be determined by evaluating the slope of the tangent to the VTC at the bias point Q,

$$A_{v} = \frac{dv_{DS}}{dv_{GS}} \bigg|_{v_{GS} = V_{GS}}$$

(6.13)

Utilizing Eq. (6.5) we obtain

$$A_{v} = -k_{n}(V_{GS} - V_{t})R_{D}$$

(6.14)

which can be expressed in terms of the overdrive voltage at the bias point,  $V_{OV}$ , as

$$A_v = -k_n V_{OV} R_D \tag{6.15}$$

We make the following observations on this expression for the voltage gain.

- 1. The gain is negative, which signifies that the amplifier is inverting; that is, there is a 180° phase shift between the input and the output. This inversion is obvious in Fig. 6.4(b) and should have been anticipated from Eq. (6.5).

- 2. The gain is proportional to the load resistance  $R_D$ , to the transistor transconductance parameter  $k_n$ , and to the overdrive voltage  $V_{OV}$ . This all makes intuitive sense.

#### 342 Chapter 6 Transistor Amplifiers

Another simple and insightful expression for the voltage gain  $A_v$  can be derived by recalling that the dc current in the drain at the bias point is related to  $V_{OV}$  by

$$I_D = \frac{1}{2}k_n V_{OV}^2$$

This equation can be combined with Eq. (6.15) to obtain

$$A_{v} = -\frac{I_{D}R_{D}}{V_{OV}/2}$$

(6.16)

That is, the gain is simply the ratio of the dc voltage drop across the load resistance  $R_D$  to  $V_{OV}/2$ . It can be expressed in the alternative form

$$A_{v} = -\frac{V_{DD} - V_{DS}}{V_{OV}/2}$$

(6.17)

Since the maximum slope of the VTC in Fig. 6.4(b) occurs at point B, the maximum gain magnitude  $|A_{ymax}|$  is obtained by biasing the transistor at point B,

$$|A_{v \max}| = \frac{V_{DD} - V_{DS}|_{B}}{V_{OV}|_{B}/2}$$

and since  $V_{DS}|_{\rm B} = V_{OV}|_{\rm B}$ ,

$$|A_{v\max}| = \frac{V_{DD} - V_{OV}|_{B}}{V_{OV}|_{B}/2}$$

(6.18)

where  $V_{OV}|_{\rm B}$  is given by Eq. (6.7). Of course, this result is only of theoretical importance since biasing at B would leave no room for negative signal swing at the output. Nevertheless, the result in Eq. (6.18) is valuable as it provides an upper bound on the magnitude of voltage gain achievable from this basic amplifier circuit. As an example, for a discrete-circuit amplifier operated with  $V_{DD} = 5 \text{ V}$  and  $V_{OV}|_{\rm B} = 0.5 \text{ V}$ , the maximum achievable gain is 18 V/V. An integrated-circuit amplifier utilizing a modern submicron MOSFET operated with  $V_{DD} = 1.3 \text{ V}$  and with  $V_{OV}|_{\rm B} = 0.2 \text{ V}$  realizes a maximum gain of 11 V/V.

Finally, note that to maximize the gain, the bias point Q should be as close to point B as possible, consistent with the required signal swing at the output. This point will be explored further in the end-of-chapter problems.

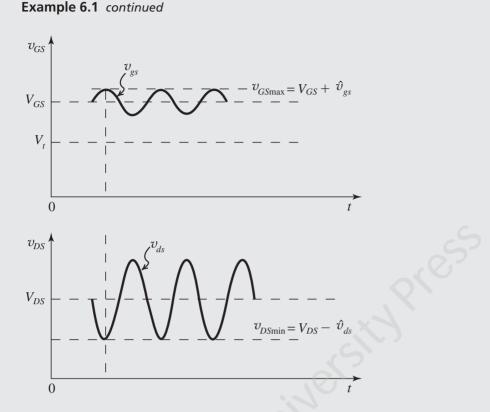

## Example 6.1

Consider the amplifier circuit shown in Fig. 6.4(a). The transistor is specified to have  $V_t = 0.4$  V,  $k'_n = 0.4$  mA/V<sup>2</sup>, W/L = 10, and  $\lambda = 0$ . Also, let  $V_{DD} = 1.8$  V,  $R_D = 17.5$  k $\Omega$ , and  $V_{GS} = 0.6$  V.

- (a) For  $v_{gs} = 0$  (and hence  $v_{ds} = 0$ ), find  $V_{OV}$ ,  $I_D$ ,  $V_{DS}$ , and  $A_v$ .

- (b) What is the maximum symmetrical signal swing allowed at the drain? Hence, find the maximum allowable amplitude of a sinusoidal  $v_{es}$ .

#### Example 6.1 continued

#### **Solution**

(a) With  $V_{GS} = 0.6$  V,  $V_{OV} = 0.6 - 0.4 = 0.2$  V. Thus,

$$I_{D} = \frac{1}{2}k'_{n}\left(\frac{W}{L}\right)V_{OV}^{2}$$

=  $\frac{1}{2} \times 0.4 \times 10 \times 0.2^{2} = 0.08 \text{ mA}$

$V_{DS} = V_{DD} - R_{D}I_{D}$

=  $1.8 - 17.5 \times 0.08 = 0.4 \text{ V}$

Since  $V_{DS}$  is greater than  $V_{OV}$ , the transistor is indeed operating in saturation. The voltage gain can be found from Eq. (6.15),

$$A_v = -k_n V_{OV} R_D$$

= -0.4 × 10 × 0.2 × 17.5 = -14 V/V

An identical result can be found using Eq. (6.17).

(b) Since  $V_{ov} = 0.2$  V and  $V_{DS} = 0.4$  V, we see that the maximum allowable negative signal swing at the drain is 0.2 V. In the positive direction, a swing of +0.2 V would not cause the transistor to cut off (since the resulting  $v_{DS}$  would be still lower than  $V_{DD}$ ) and thus is allowed. Thus the maximum symmetrical signal swing allowable at the drain is  $\pm 0.2$  V. The corresponding amplitude of  $v_{es}$  can be found from

$$\hat{v}_{gs} = \frac{\hat{v}_{ds}}{|A_v|} = \frac{0.2 \text{ V}}{14} = 14.2 \text{ mV}$$

Since  $\hat{v}_{es} \ll V_{ov}$ , the operation will be reasonably linear (more on this in later sections).

Greater insight into the issue of allowable signal swing can be obtained by examining the signal waveforms shown in Fig. 6.5. Note that for the MOSFET to remain in saturation at the negative peak of  $v_{ds}$ , we must ensure that

$$v_{DSmin} \ge v_{GSmax} - V_t$$

that is,

$$0.4 - |A_v| \hat{v}_{gs} \ge 0.6 + \hat{v}_{gs} - 0.4$$

which results in

$$\hat{v}_{gs} \le \frac{0.2}{|A_v| + 1} = 13.3 \text{ mV}$$

This result differs slightly from the one obtained earlier.

**Figure 6.5** Signal waveforms at gate and drain for the amplifier in Example 6.1. Note that to ensure operation in the saturation region at all times,  $v_{DSmin} \ge v_{GSmax} - V_t$ .

#### EXERCISE

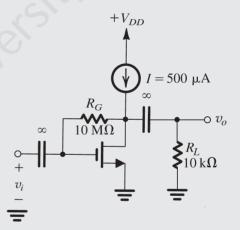

amplifier shown in Fig. 6.6,

**D6.2** For the amplifier circuit studied in Example 6.1, create two alternative designs, each providing a voltage gain of -10 by (a) changing  $R_D$  while keeping  $V_{OV}$  constant and (b) changing  $V_{OV}$  while keeping  $R_D$  constant. For each design, specify  $V_{GS}$ ,  $I_D$ ,  $R_D$ , and  $V_{DS}$ . **Ans.** (a) 0.6 V, 0.08 mA, 12.5 k $\Omega$ , 0.8 V; (b) 0.54 V, 0.04 mA, 17.5 k $\Omega$ , 1.1 V

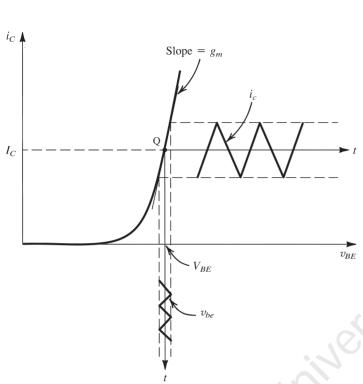

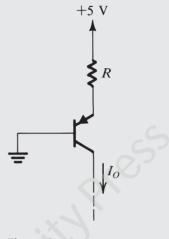

The BJT Case A similar development can be used to obtain the small-signal voltage gain of the BJT

$$A_{v} = \frac{dv_{CE}}{dv_{BE}}\Big|_{v_{BE} = V_{BE}}$$

(6.19)

Utilizing Eq. (6.9) together with Eq. (6.12), we obtain

$$A_v = -\left(\frac{I_C}{V_T}\right) R_C \tag{6.20}$$

**Figure 6.6** BJT amplifier biased at a point Q, with a small voltage signal  $v_{be}$  superimposed on the dc bias voltage  $V_{BE}$ . The resulting output signal  $v_{ce}$  appears superimposed on the dc collector voltage  $V_{CE}$ . The amplitude of  $v_{ce}$  is larger than that of  $v_{be}$  by the voltage gain  $A_{v}$ . We make the following observations on this expression for the voltage gain:

- 1. The gain is negative, which signifies that the amplifier is inverting; that is, there is a  $180^{\circ}$  phase shift between the input and the output. This inversion should have been anticipated from Eq. (6.9).

- **2.** The gain is proportional to the collector bias current  $I_c$  and to the load resistance  $R_c$ .

Additional insight into the voltage gain  $A_v$  can be obtained by expressing Eq. (6.20) as

$$A_v = -\frac{I_C R_C}{V_T} \tag{6.21}$$

That is, the gain is the ratio of the dc voltage drop across the load resistance  $R_c$  to the physical constant  $V_T$  (recall that the thermal voltage  $V_T \simeq 25 \text{ mV}$  at room temperature). This relationship is similar in form to that for the MOSFET (Eq. 6.16) except that here the denominator is a physical constant ( $V_T$ ) rather than a design parameter ( $V_{OV}/2$ ). Usually,  $V_{OV}/2$  is larger than ( $V_T$ ), thus we can obtain higher voltage gain from the BJT amplifier than from the MOSFET amplifier. This should not be surprising, as the exponential  $i_C - v_{BE}$  relationship is much steeper than the square-law relationship  $i_D - v_{GS}$ .

The gain  $A_v$  in Eq. (6.21) can be expressed alternately as

$$A_{v} = -\frac{V_{CC} - V_{CE}}{V_{T}}$$

(6.22)

from which we see that maximum gain is achieved when  $V_{CE}$  is at its minimum value of about 0.3 V,

$$|A_{v\max}| = \frac{V_{CC} - 0.3}{V_T} \tag{6.23}$$

Here again, this is only a theoretical maximum, since biasing the BJT at the edge of saturation leaves no room for negative signal swing at the output. Equation (6.23) nevertheless provides an upper bound on the voltage gain achievable from the basic BJT amplifier. As an example, for  $V_{CC} = 5$  V, the maximum gain is 188 V/V, considerably larger than in the MOSFET case. For modern low-voltage technologies, a  $V_{CC}$  of 1.3 V provides a gain of 40 V/V, again much larger than the MOSFET case. The reader should not, however, jump to the conclusion that the BJT is preferred to the MOSFET in the design of modern integrated-circuit amplifiers; in fact, the opposite is true, as we shall see in Chapter 7 and beyond.

Finally, we conclude from Eq. (6.22) that to maximize  $|A_v|$  the transistor should be biased at the lowest possible  $V_{CE}$  consistent with the desired value of negative signal swing at the output.

# Example 6.2

Consider an amplifier circuit using a BJT having  $I_s = 10^{-15}$  A, a collector resistance  $R_c = 6.8$  k $\Omega$ , and a power supply  $V_{cc} = 10$  V.

#### Example 6.2 continued

- (a) Determine the value of the bias voltage  $V_{BE}$  required to operate the transistor at  $V_{CE} = 3.2$  V. What is the corresponding value of  $I_C$ ?

- (b) Find the voltage gain  $A_v$  at this bias point. If an input sine-wave signal of 5-mV peak amplitude is superimposed on  $V_{BE}$ , find the amplitude of the output sine-wave signal (assume linear operation).

- (c) Find the positive increment in  $v_{BE}$  (above  $V_{BE}$ ) that drives the transistor to the edge of saturation, where  $v_{CE} = 0.3$  V.

- (d) Find the negative increment in  $v_{BE}$  that drives the transistor to within 1% of cutoff (i.e., to  $v_{CE} = 0.99V_{CC}$ ).

#### Solution

(a)

$$I_C = \frac{V_{CC} - V_{CE}}{R_C} = \frac{10 - 3.2}{6.8} = 1 \text{ mA}$$

The value of  $V_{BE}$  can be determined from

$$1 \times 10^{-3} = 10^{-15} e^{V_{BE}/V_T}$$

(00 0 ... T

which results in

(b)

$$A_v = -\frac{V_{cc} - V_{cE}}{V_T} = \frac{10 - 3.2}{0.025} = -272 \text{ V/V}$$

$$\hat{v}_{ce} = 272 \times 0.005 = 1.36 \text{ V}$$

(c) For  $v_{CE} = 0.3$  V,

$$i_c = \frac{10 - 0.3}{6.8} = 1.617 \text{ mA}$$

To increase  $i_C$  from 1 mA to 1.617 mA,  $v_{BE}$  must be increased by

$$\Delta v_{BE} = V_T \ln\left(\frac{1.617}{1}\right) = 12 \text{ mV}$$

(d) For

$$v_{CE} = 0.99 V_{CC} = 9.9 V$$

$$i_c = \frac{10 - 9.9}{6.8} = 0.0147 \text{ mA}$$

To decrease  $i_C$  from 1 mA to 0.0147 mA,  $v_{BE}$  must change by

$$\Delta v_{BE} = V_T \ln\left(\frac{0.0147}{1}\right) = -105.5 \text{ mV}$$

#### **EXERCISE**

**6.3** For the situation described in Example 6.2, while keeping  $I_c$  unchanged at 1 mA, find the value of  $R_c$  that will result in a voltage gain of -320 V/V. What is the largest negative signal swing allowed at the output (assume that  $v_{CE}$  is not to decrease below 0.3 V)? What (approximately) is the corresponding input signal amplitude? (Assume linear operation.)

**Ans.** 8 kΩ; 1.7 V; 5.3 mV

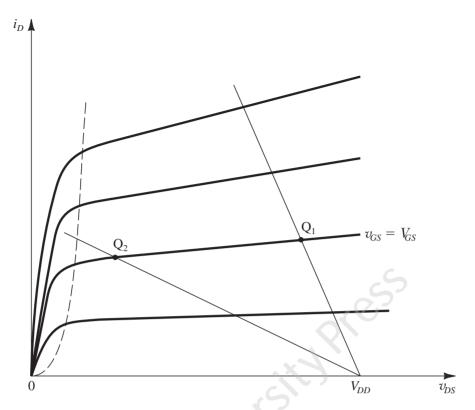

Figure 6.7 Graphical construction to determine the voltage-transfer characteristic of the amplifier in Fig. 6.4(a).

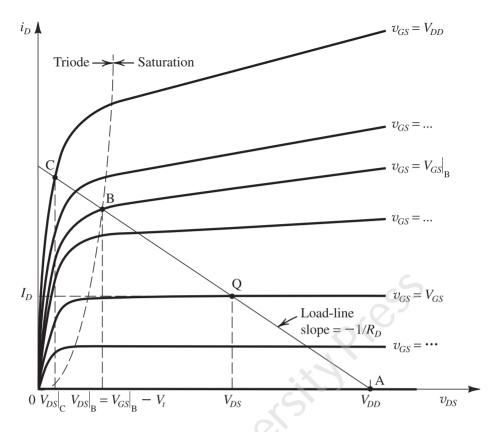

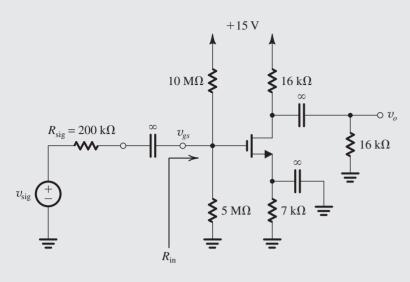

# 6.1.6 Determining the VTC by Graphical Analysis

Figure 6.7 shows a graphical method for determining the VTC of the amplifier of Fig. 6.4(a). Although graphical analysis of transistor circuits is rarely employed in practice, it is useful to us at this stage for gaining greater insight into circuit operation, especially in answering the question of where to locate the bias point Q.

The graphical analysis is based on the observation that for each value of  $v_{GS}$ , the circuit will be operating at the point of intersection of the  $i_D - v_{DS}$  graph corresponding to the particular value of  $v_{GS}$  and the straight line representing Eq. (6.3), which can be rewritten in the form

$$i_D = \frac{V_{DD}}{R_D} - \frac{1}{R_D} v_{DS}$$

(6.24)