# FIFTH EDITION

# S. Salivahanan

Principal, SSN College of Engineering Chennai

# S. Arivazhagan

Principal, Mepco Schlenk Engineering College Sivakasi

#### OXFORD UNIVERSITY PRESS

Oxford University Press is a department of the University of Oxford. It furthers the University's objective of excellence in research, scholarship, and education by publishing worldwide. Oxford is a registered trade mark of Oxford University Press in the UK and in certain other countries.

Published in India by Oxford University Press Ground Floor, 2/11, Ansari Road, Daryaganj, New Delhi 110002, India

© Oxford University Press 2018 Previous editions published by Vikas Publishing House Pvt. Ltd

The moral rights of the author/s have been asserted.

Fifth Edition published in 2018

All rights reserved. No part of this publication may be reproduced, stored in a retrieval system, or transmitted, in any form or by any means, without the prior permission in writing of Oxford University Press, or as expressly permitted by law, by licence, or under terms agreed with the appropriate reprographics rights organization. Enquiries concerning reproduction outside the scope of the above should be sent to the Rights Department, Oxford University Press, at the address above.

> You must not circulate this work in any other form and you must impose this same condition on any acquirer.

> > ISBN-13: 978-0-19-948868-1 ISBN-10: 0-19-948868-1

Typeset in Times by P.N. Computers, New Delhi Printed in India by Magic International (P) Ltd., Greater Noida

Cover image: deepadesigns/Shutterstock

Third-party website addresses mentioned in this book are provided by Oxford University Press in good faith and for information only. Oxford University Press disclaims any responsibility for the material contained therein.

# **Preface to the Fifth Edition**

Digital electronic circuits are mainly based on digital design. Today, digital circuits form the workhorses of the mobile phone, smart TV, digital camera, computer, GPS, and many other applications that demand digital electronic circuitry. Ever since the invention of transistors in 1947, there has been a growing dependency on digital electronic devices in our day-to-day life. The usage of system-based design tools from the mid-1980s has revolutionized the electronic industry worldwide. The functionality of any digital circuit can be written using a hardware description language (HDL) such as Verilog or VHDL and it can be synthesized into hardware using FPGA or CMOS technology. Every digital device in future will be smart enough to automatically communicate with other devices and also do work without human intervention. Moreover, any technological advancement in industry finds its way to engineering curriculum. This book provides an exposition of the fundamental concepts for the design of digital circuits in all disciplines of engineering has created an urge among students to have an in-depth knowledge about digital circuits and design.

# About the Book

A single textbook dealing with the basics of digital technology including the design aspects of digital circuits is the need of the day. We present this fifth edition to fulfil the requirements of the students of various B.E./B.Tech. degree courses, including Electronics and Communication Engineering, Electrical and Electronics Engineering, Information Technology, Computer Science and Engineering, and Electronics and Instrumentation Engineering offered in all Indian universities. It will also serve as textbook for students of B.Sc. and M.Sc. degree courses in Electronics, Information Technology, Computer Science, Applied Physics and Computer Software, and MCA, AMIE, Grad. IETE, and Diploma courses, and as a reference book for competitive examinations. All the topics have been illustrated with clear diagrams. A variety of examples is given to enable students to design digital circuits efficiently.

# **Key Features**

- Provides simple and clear explanation of digital electronic concepts in a lucid language.

- Includes numerous examples—each solved step-by-step in chapters.

- Numerous review questions and additional problems are given at the end of each chapter to help reader apply and practice the concepts learnt.

# New to this Edition

- Introduces newer topics such as SDRAM, DDR RAMs, Flash memories, and GAL.

- Includes more solved problems using Boolean algebra, six-variable K-map, Quine-McClusky method, more logic function implementation using multiplexers, minimization of state diagram using merger graph, and also additional problems for analysis of sequence cells.

- Presents Verilog HDL programs in addition to VHDL programs.

# Organization of the Book

This book is divided into 16 chapters. Each chapter begins with an introduction and ends with review questions and problems.

Chapter 1 provides an introduction to the number system and binary arithmetic and codes.

**Chapter 2** deals with Boolean algebra, simplification using Boolean theorems, K-map method, and Quine-McCluskey method.

**Chapter 3** discusses logic gates and implementation of switching functions using basic and universal gates.

Chapter 4 deals with various logic families such as TTL and CMOS logic circuits.

Chapters 5 and 6 give a brief description on combinational circuits like arithmetic and data processing.

Chapter 7 describes flip-flops and realization using flip-flops.

Chapter 8 discusses synchronous and asynchronous counters and the design of synchronous counters in detail.

Chapter 9 presents shift registers, shift counters, and ring counters and their design.

Chapter 10 elaborates upon memory devices, which include ROM, RAM, PLA, PAL, and FPGA.

Chapters 11 and 12 are devoted to the design of synchronous and asynchronous sequential circuits, respectively.

Chapter 13 explains some of the most common types of digital to analog and analog to digital converters.

Chapters 14 and 15 deal with clock generators and applications of digital circuits, respectively.

Chapter 16 describes hardware description language (HDL) for digital circuits.

An appendix provides a table of 74XX series TTL gates.

# Acknowledgements

We sincerely thank the managements of SSN College of Engineering, Chennai and Mepco Schlenk Engineering College, Sivakasi, for their constant encouragement and providing the necessary facilities for completing this project. We express our deep gratitude to Prof. M. Salihu, Former Vice-Chancellor, Madurai Kamaraj University, for writing Foreword to the first edition of this book. Many of our colleagues have reviewed the additional material and we thank them for their useful comments, which have improved the book considerably over the previous edition. Our thanks are due to Mr. R. Gopalakrishnan, Mr. K. Rajan, and Mr. A. Chakkarapani for word processing the additional script.

We specially thank Oxford University Press for their initiation to bring out this revised edition in a short span of time.

Dr Salivahanan is greatly thankful to his wife, Kalavathy and sons, Santhosh Kanna and Subadesh Kanna. Dr Arivazhagan expresses his heartfelt thanks to his wife Rosilin Glory and children Sri Madhu Mitha and Selva Yokesh.

We welcome suggestions for the improvement of the book.

S. Salivahanan S. Arivazhagan

# Contents

iv

v

1

Foreword to the First Edition Preface to the Fifth Edition 1. Number System and Codes 1.1 Introduction 1 1.2 Number System 1 1.2.1 Binary Numbers 1 1.2.2 Decimal–Binary Conversion 2 1.2.3 Octal Numbers 3 1.2.4 Octal–Binary Conversion 4 1.2.5 Hexadecimal Numbers 5 1.2.6 Hexadecimal-Binary Conversion 6 1.2.7 Hexadecimal–Octal Conversion 7 1.3 Floating Point Representation of Numbers - 9 1.4 Arithmetic Operation 10 1.4.1 Binary Arithmetic 10 1.5 l's and 2's Complements 13 1.5.1 l's Complement Subtraction 13 1.5.2 2's Complement Subtraction 14 1.5.3 Signed Binary Number Representation 15 1.5.4 Addition in the 2's Complement System 16 1.5.5 Subtraction in the 2's Complement System 17 1.5.6 Arithmetic Overflow 18 1.5.7 Comparison Between 1's and 2's Complements 19 1.6 9's Complement 19 1.6.1 9's Complement Subtraction 20 10's Complement 20 1.7 1.7.1 10's Complement Subtraction 21 1.8 Binary Coded Decimal (BCD) 22 1.8.1 BCD Addition 22 1.8.2 BCD Subtraction 23 1.9 Codes 25 1.9.1 Weighted Binary Codes 25 1.9.2 Non-weighted Codes 27 1.9.3 Error Detecting Codes 31 1.9.4 Error Correcting Codes 32 1.9.5 Alphanumeric Codes 33 Review Questions 36

Problems 36

viii Contents

# 2. Boolean Algebra and Minimization Techniques

- 2.1 Introduction 40

- 2.2 Development of Boolean Algebra 40

- 2.3 Boolean Logic Operations 40

- 2.3.1 Logical AND Operation 41

- 2.3.2 Logical OR Operation 41

- 2.3.3 Logical Complementation (Inversion) 41

- 2.4 Basic Laws of Boolean Algebra 41

- 2.4.1 Boolean Addition 42

- 2.4.2 Boolean Multiplication 42

- 2.4.3 Properties of Boolean Algebra 42

- 2.4.4 Principle of Duality 44

- 2.5 Demorgan's Theorems 45

- 2.6 Sum of Products and Product of Sums 53

- 2.6.1 Minterm 54

- 2.6.2 Maxterm 56

- 2.6.3 Deriving Sum of Product (SOP) Expression from a Truth Table 59

- 2.6.4 Deriving Product of Sum (POS) Expression from a Truth Table 59

- 2.7 Karnaugh Map 60

- 2.7.1 Five-variable K-map 68

- 2.7.2 Six-variable K-map 72

- 2.8 Quine-McCluskey or Tabular Method of Minimization of Logic Functions 74

Review Questions 85 Problems 86

# 3. Logic Gates

- 3.1 Introduction 90

- 3.2 Positive and Negative Logic Designation 90

- 3.3 Logic Gates 91

- 3.3.1 OR Gate 91

- 3.3.2 AND Gate 93

- 3.3.3 NOT Gate (Inverter) 94

- 3.3.4 NAND Gate 95

- 3.3.5 NOR Gate 96

- 3.3.6 Universal Gates/Universal Building Blocks 96

- 3.3.7 Exclusive-OR (Ex-OR) Gate 99

- 3.3.8 Exclusive-NOR (Ex-NOR) Gate 101

- 3.4 Mixed Logic 110

- 3.4.1 Basic Mixed Logic Operators 111

- 3.4.2 Mixed Logic Symbols/Alternate GATE Symbols 112

- 3.4.3 Assertion Levels and Polarity Indication 113

- 3.5 Multilevel Gating Networks 115

- 3.5.1 Implementation of Multilevel Gate Network 115

- 3.5.2 Conversion to NAND-NAND and NOR-NOR Gate Networks 116

- 3.6 Multiple Output Gate Networks 124

3.6.1 BCD to Excess-3 Code Conversion 124 Review Questions 126

# 4. Logic Families

| 4.1 | Introduction | 12 |

|-----|--------------|----|

| 4.1 | Introduction | 12 |

- 4.2 Digital Integrated Circuits 1284.2.1 Bipolar Logic Families 128

- 4.2.2 MOS Families 129

- 4.3 Characteristics of Digital ICs 129

- 4.3.1 Speed of Operation 129

- 4.3.2 Power Dissipation 130

- 4.3.3 Fan-in 130

- 4.3.4 Fan-out 130

- 4.3.5 Noise Immunity or Noise Margin 130

- 4.3.6 Operating Temperature 131

- 4.3.7 Power Supply Requirements 131

- 4.3.8 Current and Voltage Parameters 131

- 4.4 Current-Sourcing and Current-Sinking Logic 131

- 4.5 Resistor-Transistor Logic (RTL) 131

- 4.6 Resistor-Capacitor-Transistor Logic (RCTL) 133

- 4.7 Diode–Transistor Logic (DTL) 134

- 4.8 High Threshold Logic (HTL) 135

- 4.9 Transistor–Transistor Logic (TTL or T2L) 135

- 4.9.1 TTL NAND Gate 136

- 4.9.2 Other TTL Series 137

- 4.9.3 TTL Circuit Output Connections 138

- 4.9.4 TTL Parameters 141

- 4.9.5 TTL Inverter 147

- 4.9.6 TTL NOR Gate 147

- 4.9.7 TTL AND and OR Gate 148

- 4.10 Emitter-coupled Logic (ECL)—Non-saturating Logic 149 4.10.1 ECL OR/NOR Gate 151

- 4.10.2 ECL Characteristics 151

- 4.11 Integrated-injection Logic (I2L) 152

- 4.12 MOS Digital Integrated Circuits 153

- 4.12.1 MOSFET 153

- 4.12.2 MOSFET Logic Circuits 154

- 4.12.3 Characteristics of MOS Logic 157

- 4.13 Complementary MOS Logic 157

- 4.13.1 CMOS Inverter 157

- 4.13.2 CMOS NAND Gate (74C00) 158

- 4.13.3 CMOS NOR Gate 159

- 4.13.4 CMOS Series 159

- 4.14 Characteristics of CMOS 160

ĸ

#### Contents

4.15 BiCMOS Logic Circuits 161

- 4.16 Compatibility or Interfacing 163

4.16.1 Interfacing CMOS with TTL 164

4.16.2 TTL Driving CMOS 164

4.16.3 CMOS Driving TTL 165

- 4.17 Comparison of Logic Gates 166

Review Questions 170 Problems 171

# 5. Arithmetic Circuits

| 5.1 | Introduction | 173 |

|-----|--------------|-----|

|     |              |     |

- 5.2 Procedure for the Design of Combinational Circuits 173

- 5.3 Half-Adder 173

- 5.4 Full-Adder 175

- 5.5 K-Map Simplification 177

- 5.6 Half-Subtractor 178

- 5.7 Full-Subtractor 178

- 5.8 Parallel Binary Adder 180

5.8.1 IC 7483 4-bit Parallel Binary Adder 182

5.8.2 4-bit Parallel Binary Subtractor 183

- 5.9 Controlled Inverter 183

- 5.10 4-bit Parallel Adder / Subtractor 184

- 5.11 Fast Adder 185 5.11.1 4-bit Carry Look Ahead Adder 185

- 5.12 Serial Adder 188

- 5.13 Serial Subtraction Using 2's Complement 189

- 5.14 4-bit Serial Adder/Subtractor 189

- 5.15 BCD Adder 190

- 5.16 Binary Multiplier 1935.16.1 Multiplier Using Shift Method 1945.16.2 Parallel Multiplier 194

- 5.17 Binary Divider 196

Review Questions 198

# 6. Combinational Circuits

- 6.1 Introduction 199

- 6.2 Multiplexers (Data Selectors) 199

- 6.2.1 Basic Four-input Multiplexer 200

- 6.2.2 IC 74151 8-to-1 Multiplexer 201

- 6.2.3 IC 74150 16-to-1 Multiplexer 202

- 6.2.4 Implementation of Higher Order Multiplexers 205

- 6.2.5 Implementation of Boolean Expression Using Multiplexers 206

- 6.3 Applications of Multiplexer 208

- 6.4 Demultiplexers (Data Distributors) 216

173

- 6.4.1 l-to-4 Demultiplexer 216

- 6.4.2 1-to-8 Demultiplexer 217

- 6.4.3 IC 74154 1-to-16 Demultiplexer 218

- 6.5 Decoders 220

- 6.5.1 Basic Binary Decoder 220

- 6.5.2 3-to-8 Decoder 220

- 6.5.3 4-to-16 Decoder 222

- 6.5.4 IC 74139 Dual 2-to-4 Decoder 223

- 6.5.5 IC74154 4-to-16 Decoder 223

- 6.5.6 BCD-to-Decimal Decoder 225

- 6.5.7 IC 7445 BCD-to-Decimal Decoder 226

- 6.5.8 Implementation of Higher Order Decoders Using Lower Order Decoders 227

- 6.5.9 BCD-to-Seven-Segment Decoder/Driver 228

- 6.6 Liquid Crystal Displays 234

- 6.7 Encoders 235

- 6.7.1 Octal-to-Binary Encoder 236

- 6.7.2 Decimal-to-BCD Encoder 237

- 6.7.3 Priority Encoder 238

- 6.7.4 IC 74148 8-to-3 Priority Encoder 239

- 6.7.5 IC 74147—Decimal-to-BCD Priority Encoder 240

- 6.8 Parity Generators/Checkers 2436.8.1 Design of Parity Checkers 243

- 6.9 Parity Generation 2446.9.1 Odd-parity Generator 244

- 6.10 Code Converters 248

- 6.10.1 BCD-to-Binary Converters 249

- 6.10.2 Binary-to-Gray Code Converters 252

- 6.10.3 Gray Code-to-Binary Converters 254

- 6.11 Magnitude Comparator 257

- 6.11.1 4-bit Magnitude Comparator 259

- 6.11.2 IC 7485—4-bit Magnitude Comparator 260

- 6.11.3 Cascading of IC 7485s 262

- 6.12 Applications of Comparators 262

- Review Questions 262

- Problems 263

# 7. Flip-Flops

- 7.1 Introduction 267

- 7.2 Latches 268

- 7.2.1 Set-Reset (S-R) Latch 269

- 7.2.2 NOR-based S-R Latch 269

- 7.2.3 NAND-based S-R Latch 271

- 7.2.4 State Diagram and Characteristic Equation of S-R Latch 272

Contents

|    | 7.3        | Flip–Flops 273                                                       |

|----|------------|----------------------------------------------------------------------|

|    |            | 7.3.1 Types of Flip-Flops 273                                        |

|    | 7.4        | S-R Flip-Flop 273                                                    |

|    | 7.5        | D Flip-Flop 276                                                      |

|    |            | 7.5.1 State Diagram and Characteristic Equation of D Flip-Flop 277   |

|    | 7.6        | J-K Flip-Flop 278                                                    |

|    |            | 7.6.1 State Diagram and Characteristic Equation of J-K Flip-Flop 280 |

|    | 7.7        | T Flip-Flop 281                                                      |

|    |            | 7.7.1 State Diagram and Characteristic Equation of T Flip-Flop 282   |

|    | 7.8        | Triggering of Flip-Flops 283                                         |

|    |            | 7.8.1 Level Triggering in Flip-Flops 284                             |

|    |            | 7.8.2 Edge Triggering in Flip-Flops 284                              |

|    |            | 7.8.3 Edge-triggered D Flip-Flop 285                                 |

|    |            | 7.8.4 Edge-triggered J-K Flip-Flop 286                               |

|    | 7.9        | Asynchronous Inputs in Flip-Flops 287                                |

|    | 7.10       | Master–Slave Flip-Flops 288                                          |

|    |            | 7.10.1 The Race-around Condition 288                                 |

|    |            | 7.10.2 Master-Slave J-K Flip-Flop 289                                |

|    | 7.11       | Realisation of One Flip-Flop Using Other Flip-Flops 290              |

|    |            | 7.11.1 Realisation of Delay Flip-Flop Using S-R Flip-Flop 291        |

|    |            | 7.11.2 Realisation of J-K Flip-Flop Using S-R Flip-Flop 292          |

|    |            | 7.11.3 Realisation of Trigger Flip-Flop Using S-R Flip-Flop 295      |

|    |            | 7.11.4 Realisation of Delay Flip-Flop Using J-K Flip-Flop 296        |

|    |            | 7.11.5 Realisation of J-K Flip-Flop Using D Flip-Flop 298            |

|    | 7.12       | Applications of Flip-Flops 299                                       |

|    |            | 7.12.1 Parallel Data Storage 300                                     |

|    |            | 7.12.2 Shift Registers 301                                           |

|    |            | 7.12.3 Frequency Division 301                                        |

|    |            | 7.12.4 Counters 302                                                  |

|    | Revie      | ew Questions 302                                                     |

|    |            | lems 303                                                             |

| 8. | Cou        | inters                                                               |

| -  | 8.1        | Introduction 307                                                     |

|    | 8.1<br>8.2 | Asynchronous (Ripple or Serial) Counter 307                          |

|    | 0.2        | Asynchronous (Apple of Serial) Counter 50/                           |

- Asynchronous (Ripple or Serial) Counter 307 8.2

- 8.3 Ripple Counter with Decoded Outputs 309

- 8.4 Ripple Counters with Modulus  $< 2^n - 312$

- 8.5 Counter ICs 313 8.5.1 IC 7493 — 4-bit Binary Ripple Counter 313 8.5.2 IC 7490 — Decade Counter 315

- 8.6 Asynchronous Down Counter 316

- 8.7 Up-Down Counter 317

- 8.8 Propagation Delay in Ripple Counter 319

- 8.9 Synchronous (Parallel) Counter 319

307

#### xii

- 8.10 Synchronous Counter with Ripple Carry 321

- 8.11 Synchronous Down Counter 322

- 8.12 Synchronous Up/Down Counter 323

- 8.13 Synchronous/Asynchronous Counter 323

- 8.14 Presettable (Programmable) Counters 324

- 8.15 Design of Synchronous Counters 324

- 8.15.1 Design of MOD-3 Counter 325

- 8.15.2 Design of MOD-6 Counter 327

- 8.15.3 Design of BCD or Decade (MOD-10) Counter 329

- 8.15.4 Design of MOD-6 Unit Distance Code Counter 334

- 8.15.5 Design of MOD-8 Up-Down Counter 338

- 8.15.6 Design of Synchronous Counter Using SR, JK, T and D Flip-Flops 343

- 8.16 Counter Implementation and Applications 350

- 8.16.1 Frequency Counter 350

- 8.16.2 Measurement of Period 351

- 8.16.3 Digital Clock 352

Review Questions 353

Problems 354

# 9. Registers

- 9.1 Introduction 358

- 9.1.1 4-bit Shift Register 358

#### 9.2 Shift Registers 359

- 9.2.1 Serial-in-Serial-out Shift Register 360

- 9.2.2 IC 7491 —8-bit Serial-in-Serial-out Shift Register 363

- 9.2.3 Serial-in-Parallel-out Shift Register 363

- 9.2.4 IC 74164 8-bit Serial-in-Parallel-out Shift Register 364

- 9.2.5 Parallel-in-Serial-out Shift Register 367

- 9.2.6 IC 74165 8-bit Serial/Parallel-in and Serial-out Shift Register 368

- 9.2.7 Parallel-in-Parallel-out Register 369

- 9.2.8 IC 74195 4-bit Serial/Parallel-in and Serial/Parallel-out Shift Register 369

- 9.3 Universal Shift Registers 371

- 9.3.1 IC 74194 4-bit Bidirectional Shift Register 372

- 9.4 Shift Register Counters 373

- 9.4.1 Ring Counter 374

- 9.4.2 Design of 4-bit Self-correcting Ring Counter 375

- 9.4.3 Ring Counter Using IC 74164 Serial Shift Register 379

- 9.5 Shift Counter/Johnson Counter 380

- 9.5.1 Design of 4-bit Self-correcting Shift Counter 381

- 9.6 Sequence Generator 385

- 9.6.1 Design of 5-bit Sequence Generator 386

- 9.6.2 Design of 6-bit Sequence Generator 387

- 9.6.3 Design of 7-bit Sequence Generator 389

9.6.4 Sequence Generator Using Multiplexer and Counter 392

9.6.5 Sequence Generator Using Counter 393

Review Questions 395 Problems 395

#### 10. Memory and Programmable Logic Devices

| 10.1 Introduction 398 | 1 | 0.1 | Introduction | 398 |

|-----------------------|---|-----|--------------|-----|

|-----------------------|---|-----|--------------|-----|

- 10.2 Classification of Memories 399

- 10.2.1 Registers, Main Memory and Secondary Memory 399

- 10.2.2 Sequential Access Memory and Random Access Memory 399

- 10.2.3 Static and Dynamic Memory 399

- 10.2.4 Volatile and Non-volatile Memory 399

- 10.2.5 Magnetic and Semiconductor Memory 400

- 10.3 Basic Memory Structure 400

- 10.4 Read Only Memory (ROM) 401

- 10.4.1 Architecture of ROM 401

- 10.4.2 Types of ROM 403

- 10.4.3 Programming Mechanisms 404

- 10.4.4 Organization of a Simple ROM 405

- 10.4.5 ROM ICs 405

- 10.4.6 ROM Access Time 409

- 10.4.7 Applications of ROM 409

- 10.4.8 Combinational Logic Design Using ROM 410

- 10.4.9 Programmable ROM (PROM) 414

- 10.4.10 PROM Programming 416

- 10.4.11 Erasable Programmable ROM (EPROM) 418

- 10.4.12 Programming of EPROM 419

- 10.4.13 Electrically Erasable Programmable ROM (EEPROM) 421

- 10.5 Random Access Memory (RAM) 422

- 10.5.1 Types of RAM 422

- 10.5.2 Static RAM 423

- 10.5.3 Static RAM ICs 425

- 10.5.4 Dynamic RAM (DRAM) 428

- 10.5.5 Pseudo Static RAM (PSRAM) 432

- 10.5.6 Synchronous DRAM (SDRAM) 433

- 10.5.7 DDR SDRAM 435

- 10.5.8 Advantages of RAM 437

#### 10.6 Flash Memory 437

- 10.6.1 Flash Memory Cell 438

- 10.6.2 NOR Flash 439

- 10.6.3 Flash Memory Interfacing 440

- 10.6.4 NAND Flash 441

- 10.6.5 Comparison Between NAND and NOR Flash 442

- 10.6.6 Flash Memory as a Replacement for Hard Drives 442

- 10.7 Memory Decoding 443 10.7.1 Address Assignment 443

- 10.8 Memory Expansion 446

- 10.9 Programmable Logic Devices (PLD) 448

- 10.9.1 Programmable Logic Array (PLA) 450

- 10.9.2 Implementation of Combinational and Sequential Logic Using PLA 454

- 10.9.3 Application of PLAs 459

- 10.9.4 Programmable Array Logic (PAL) 459

- 10.9.5 Generic Array Logic (GAL) 462

- 10.9.6 Field Programmable Gate Array (FPGA) 464

Review Questions 469

Problems 470

#### **11. Synchronous Sequential Circuits**

- 11.1 Introduction 473

- 11.2 General Sequential Circuit Model 473

- 11.3 Classification of Sequential Circuits 474

- 11.4 Design of Synchronous Sequential Circuits 476

- 11.4.1 Design of Serial Binary Adder 477

- 11.4.2 State Reduction and Assignment 480

- 11.4.3 Design of Sequence Detectors 484

- 11.4.4 Design of Odd/Even Parity Generator 489

- 11.5 Synchronous Sequential Circuit Design Using Algorithmic State Machine (ASM) 493

- 11.5.1 Algorithmic State Machine (ASMs) 494

- 11.5.2 ASM Charts 495

- 11.5.3 Examples of ASM Charts 497

- 11.5.4 Relationship Between State Diagrams and ASM Charts 499

- 11.5.5 Procedure for Design Using ASM Charts 501

- 11.5.6 Design of Sequence Detector Using ASM Chart 501

- 11.5.7 Design of Parity-Bit Generator Using ASM Chart 504

- 11.6 Analysis of Synchronous Sequential Circuits 509

Review Questions 520

### 12. Asynchronous Sequential Circuits

- 12.1 Introduction 521

- 12.2 Design of Fundamental Mode Asynchronous Sequential Circuits 52112.2.1(a) Realization Using D Flip-Flops 527

- 12.2.1(b) Realization Using JK Flip-Flops 529

- 12.3 Design of Pulse Mode Asynchronous Sequential Circuits 534

- 12.4 Incompletely Specified State Machines 550

- 12.5 Problems in Asynchronous Circuits 551

- 12.5.1 Cycles 551

- 12.5.2 Races 552

473

- 12.5.3 Hazards 553

- 12.6 Design of Hazard Free Switching Circuits 555

12.6.1 Static Hazards Elimination 555

- 12.6.2 Dynamic Hazards Elimination 557

- 12.6.3 Essential Hazards Elimination 557

Review Questions 558

#### 13. D/A and A/D Converters

- 13.1 Introduction 560

- 13.2 Analog and Digital Data Conversions 560

- 13.3 Specifications of D/A Converter 561

- 13.4 Basic D/A Conversion Techniques 564

- 13.4.1 Weighted Resistor Type D/A Converter 565

- 13.4.2 R-2R Ladder Type D/A Converter 569

- 13.4.3 Voltage Mode R-2R Ladder 572

- 13.4.4 Inverted or Current-Mode R-2R Ladder D/A Converter 572

- 13.5 Multiplying D/A Converters (MDACs) 574

- 13.6 Sampling Process 575

- 13.7 A/D Converters 577

- 13.8 Specifications of A/D Converter 578

- 13.9 Classification of A/D Converters 581

- 13.9.1 Simultaneous Type (Flash Type) A/D Converter 582

- 13.9.2 Counter Type A/D Converter 586

- 13.9.3 Continuous Type (Servo Tracking) A/D Converter 587

- 13.9.4 Successive Approximation Type A/D Converter 589

- 13.9.5 Single Slope Type A/D Converter 592

- 13.9.6 Dual Slope Type A/D Converter 594

- 13.9.7 Analog-to-Digital Converter Using Voltage-to-Time Conversion 595

Review Questions 597

# 14. Clock Generators

- 14.1 Introduction 599

- 14.2 Astable Multivibrator 599

- 14.2.1 Astable Multivibrator Using BJT 599

- 14.2.2 General Description of IC 555 Timer 602

- 14.2.3 Astable Multivibrator Using IC 555 Timer 604

- 14.2.4 Astable Multivibrator Using NAND / NOT Gates 605

- 14.2.5 Astable Multivibrator Using NAND / NOT Gates with R Returned to Ground 606

- 14.3 Monostable Multivibrator 607

- 14.3.1 Monostable Multivibrator Using BJT 607

- 14.3.2 Monostable Multivibrator Using IC 555 Timer 610

- 14.3.3 Monostable Multivibrator Using IC 74121 612

- 14.4 Bistable Multivibrator Using BJT 613

14.5 Schmitt Trigger 615

14.5.1 Schmitt Trigger Using BJT 616

14.5.2 Schmitt Trigger Using IC 555 Timer 619

14.5.3 Schmitt Trigger Using IC 74132 620

14.6 Crystal Clock Generators 621

Review Questions 621

# **15. Applications of Digital Circuits**

| 15.1 | Introduction | 623 |

|------|--------------|-----|

|------|--------------|-----|

- 15.2 Frequency Counter 623 15.2.1 5-digit Frequency Counter 624

- 15.3 Time Meter 625 15.3.1 4-digit Time Meter 626

- 15.4 Bar Graph Display System 627

- 15.5 Multiplexed Display System 627

- 15.5.1 4-Digit Multiplexed Display System 629

- 15.5.2 Advantages of Multiplexed Display System 631

- 15.5.3 IC 74925 4-Digit Counter with Multiplexed 7-segment Display Decoder/Driver 631

- 15.6 Dot Matrix Display System 632

#### 15.7 Digital Voltmeter 632

- 15.7.1 3-digit Digital Voltmeter 636

- 15.7.2 Merits of DVM 637

- 15.7.3 Demerits of DVM 638

- 15.8 Digital Multimeter (DMM) 638

- 15.8.1 Measurement of Voltage 638

- 15.8.2 Measurement of Current 638

- 15.8.3 Measurement of Resistance 639

Review Questions 639

# 16. HDL for Digital Circuits

- 16.1 Introduction to HDL 640

- 16.2 Very High Speed Hardware Description Language (VHDL) 640

- 16.2.1 Data Flow Description 640

- 16.2.2 Structural Description 642

- 16.2.3 Simulators 644

- 16.2.4 Other Types 646

- 16.2.5 Other Operators 648

- 16.3 Behavioral Description 648

- 16.4 VHDL Libraries 654

- 16.5 VHDL Programs for Combinational Circuits 655

- 16.5.1 VHDL Programs for Logic Gates 655

- 16.5.2 Adders and Subtractors 657

- 16.5.3 Multiplexer and Demultiplexer 659

xviii

16.5.4 Encoder and Decoder 660 16.5.5 4-bit Parity Checker 661 16.5.6 4-bit Magnitude Comparator 661 16.5.7 Code Converters 662 16.6 VHDL Programs for Sequential Logic Circuits 663 16.6.1 Realization of Flip-Flops 663 16.6.2 Realization of Shift Registers 666 16.6.3 Counters 668 16.7 VHDL Program for Arithmetic Logic Unit 672 16.8 Verilog HDL 674 16.8.1 Methodology 674 16.8.2 Modules 674 16.8.3 Data Types 675 16.8.4 Integer, Real, and Time Register Data Types 676 16.8.5 Variable Declaration 676 16.8.6 Levels of Abstraction 677 16.8.7 Verilog Operator Types 677 16.9 Verilog HDL Programs for Combinational Logic Circuits 678 16.9.1 Verilog HDL Programs for Logic Gates 678 16.9.2 Adders and Subtractors 680 16.9.3 Multiplexer and Demultiplexer 681 16.9.4 Encoder and Decoder 682 16.9.5 4-bit Parity Checker 682 16.9.6 4-bit Magnitude Comparator 682 16.9.7 Code Converters 683 16.10 Verilog HDL for Sequential Logic Circuits 683 16.10.1 Realization of Flip-Flops 683 16.10.2 Realization of Shift Registers 686 16.10.3 Counters 687 16.11 Verilog Program for Arithmetic Logic Unit 690 Review Questions 691

Appendices 694 Index 711 About the Authors 717

CHAPTER

# **Arithmetic Circuits**

# 5.1 Introduction

Digital computers and calculators consist of arithmetic and logic circuits, which contain logic gates and flip-flops that add, subtract, multiply and divide binary numbers. The basic building blocks of the arithmetic unit in a digital computer are *adders*. These circuits perform operations at speeds less than  $1\mu$ s.

A digital system consists of two types of circuits, namely

- (i) Combinational logic circuit,

- (ii) Sequential logic circuit.

In a combinational circuit, the output at any time depends only on the input values at that time. In a sequential circuit, the output at any time depends on the present input values as well as the past output values. The basic building blocks of an arithmetic unit such as half-adder and full-adder are combinational circuits.

# 5.2 Procedure for the Design of Combinational Circuits

Any combinational circuit can be designed by following the design procedure given below:

- 1. From the word description of the problem, identify the inputs and outputs and draw a block diagram.

- 2. Draw a truth table such that it completely describes the operation of the circuit for different combinations of inputs.

- 3. Write down the switching expression(s) for the output(s).

- 4. Simplify the switching expression using either algebraic or K-map method.

- 5. Implement the simplified expression using logic gates.

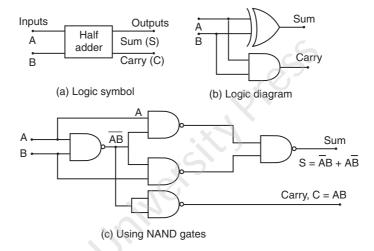

# 5.3 Half-adder

The simplest combinational circuit which performs the arithmetic addition of two binary digits is called a *half-adder*. As shown in Fig. 5.1(a), the half-adder has two inputs and two outputs. The two inputs are the two 1-bit numbers A and B, and the two outputs are the sum (S) of A and B and the carry bit denoted by C. From the truth table of the half-adder shown in Table 5.1, one can understand that the Sum output is 1 when either of the inputs (A or B) is 1, and the Carry output is 1 when both the inputs (A and B) are 1.

|  | Table 5.1 | Truth table of half-adder |

|--|-----------|---------------------------|

|--|-----------|---------------------------|

| In          | puts        | Out      | puts       |

|-------------|-------------|----------|------------|

| Augend<br>A | Addend<br>B | Sum<br>S | Carry<br>C |

| 0           | 0           | 0        | 0          |

| 0           | 1           | 1        | 0          |

| 1           | 0           | 1        | 0          |

| 1           | 1           | 0        | 1          |

Fig. 5.1 Half-adder

From Table 5.1, the logic expression for the Sum output can be written as a Sum of Product expression by summing up the input combinations for which the sum is equal to 1.

In the truth table, the sum output is 1 when AB = 01 and AB = 10. Therefore, the expression for sum is

$S = \overline{A}B + A\overline{B}$

Now, this expression can be simplified as

$S = A \oplus B$

Similarly, the logic expression for Carry output can be expressed as a Sum of Product expression by summing up the input combinations for which the carry is equal to 1. In the truth table, the carry is 1 when AB = 11. Therefore,

C = AB

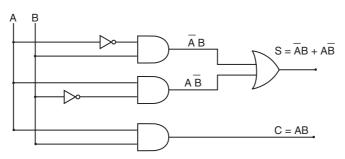

This expression for C cannot be simplified. The sum output corresponds to a logic Ex-OR function while the carry output corresponds to an AND function. So, the half-adder circuit can be implemented using Ex-OR and AND gates as shown in Fig. 5.1(b). Fig. 5.1(c) gives the realisation of the half-adder using minimum number of NAND gates. The implementation of the half-adder circuit using basic gates AND, OR and NOT is shown in Fig. 5.2.

Fig. 5.2 Half-adder using basic AND, OR and NOT gates

# 5.4 Full-adder

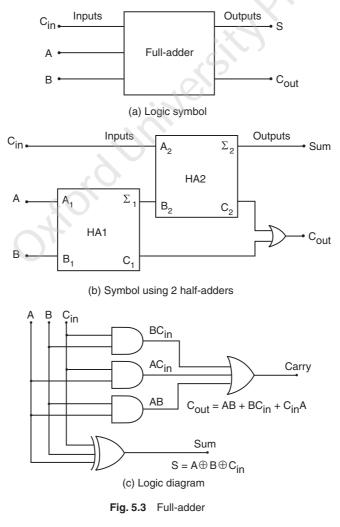

A half-adder has only two inputs and there is no provision to add a carry coming from the lower order bits when multibit addition is performed. For this purpose, a full-adder is designed. A *full-adder* is a combinational circuit that performs the arithmetic sum of three input bits and produces a sum output and a carry.

© Oxford University Press. All rights reserved.

The logic symbol of the full adder is shown in Fig.5.3(a). It consists of three inputs and two outputs. The two input variables denoted by A (Augend bit) and B (Addend bit) represent the two significant bits to be added. The third input,  $C_{in}$ , represents the carry from the previous lower significant position. The outputs are designated by the symbols S (for sum) and  $C_{out}$  (for carry). The truth table for the full-adder circuit is shown in Table 5.2. The binary variable S gives the value of the LSB of the sum, and the binary variable  $C_{out}$ , gives the output carry. A full-adder can be formed using two half-adder circuits and an OR gate as shown in Fig. 5.3 (b).

|                 | Inputs          |                                |          | puts                   |

|-----------------|-----------------|--------------------------------|----------|------------------------|

| Augend bit<br>A | Addend bit<br>B | Carry input<br>C <sub>in</sub> | Sum<br>S | Carry output $C_{out}$ |

| 0               | 0               | 0                              | 0        | 0                      |

| 0               | 0               | 1                              | 5        | 0                      |

| 0               | 1               | 0                              |          | 0                      |

| 0               | 1               | 1                              | 0        | 1                      |

| 1               | 0               | 0                              | 1        | 0                      |

| 1               | 0               | 1                              | 0        | 1                      |

| 1               | 1               | 0                              | 0        | 1                      |

| 1               | 1               | 1                              | 1        | 1                      |

| Table 5.2 | Truth table ( | of full-adder |

|-----------|---------------|---------------|

|-----------|---------------|---------------|

As shown in Table 5.2, there are eight possible input combinations for the three inputs and for each case the S and  $C_{out}$  values are listed. From the truth table, the logic expression for S can be written by summing up the input combinations for which the sum output is 1 as:

$$S = \overline{A} \overline{B} C_{\text{in}} + \overline{A} \overline{B} \overline{C}_{\text{in}} + A \overline{B} \overline{C}_{\text{in}} + A B C_{\text{in}}$$

Simplifying the above expression, we get

$$S = \overline{A}(\overline{B}C_{in} + \overline{B}C_{in}) + A(\overline{B}\overline{C}_{in} + BC_{in})$$

$$= \overline{A}(B \oplus C_{in}) + A(\overline{B} \oplus C_{in})$$

Let  $B \oplus C_{in} = X$

Now,  $S = \overline{A}X + A\overline{X} = A \oplus X$

Replacing *X* by  $B \oplus C_{in}$  in the above expression, we have

$$S = A \oplus B \oplus C_{in}$$

Similarly, the logic expression for  $C_{out}$  can be written by summing up the input combinations for which  $C_{out}$  is 1, as given below:

$$C_{out} = \overline{ABC}_{in} + \overline{ABC}_{in} + \overline{ABC}_{in} + \overline{ABC}_{in} + \overline{ABC}_{in}$$

$$= BC_{in}(A + \overline{A}) + \overline{ABC}_{in} + \overline{ABC}_{in}$$

$$= BC_{in} + \overline{ABC}_{in} + \overline{ABC}_{in}$$

Arithmetic Circuits

177

Now, the  $ABC_{in}$  term is added twice for simplification.

$$C_{\text{out}} = BC_{\text{in}} + A\overline{B}C_{\text{in}} + AB\overline{C}_{\text{in}} + ABC_{\text{in}} + ABC_{\text{in}}$$

$$= BC_{\text{in}} + AC_{\text{in}}(B + \overline{B}) + AB(C_{\text{in}} + \overline{C}_{\text{in}})$$

$$= BC_{\text{in}} + AC_{\text{in}} + AB$$

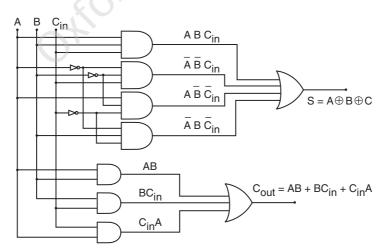

From the simplified expressions of S and  $C_{out}$ , the full-adder circuit can be implemented using one 3-input Ex-OR gate, three 2-input AND gates and one 3-input OR gate as shown in Fig. 5.3(c).

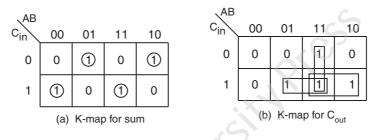

# 5.5 K-map Simplification

*K*-map method can also be used for simplifying the logic expressions for *S* and  $C_{out}$ . The *K*-maps for the outputs *S* and  $C_{out}$  are given in Fig. 5.4.

From the K-maps, the simplified expressions for S and  $C_{out}$  can be written as follows:

$$S = \overline{AB}C_{in} + \overline{AB}\overline{C}_{in} + A\overline{B}\overline{C}_{in} + ABC_{in}$$

$$C_{out} = AB + BC_{in} + C_{in}A$$

Using the above expressions, the full-adder can be implemented using basic gates as shown in Fig. 5.5.

Fig. 5.5 Full-adder using basic gates

178

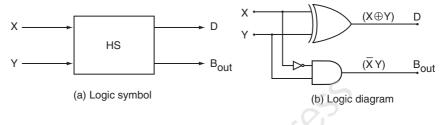

# 5.6 Half-subtractor

The half-subtractor is a combinational circuit which is used to perform subtraction of two bits. It has two inputs, X (minuend) and Y (subtrahend) and two outputs D (difference) and  $B_{out}$  (borrow out). The logic symbol for a half-subtractor is shown in Fig. 5.6(a). The truth table for half-subtractor is shown in Table 5.3. From the truth table, it is clear that the difference output is 0 if X = Y and 1 if  $X \neq Y$ ; the borrow output  $B_{out}$  is 1 whenever X < Y. If X is less than Y, then subtraction is done by borrowing 1 from the next higher order bit.

Fig. 5.6 Half-subtractor

| Table 5.5 Inum table of nall-subtracto | Table 5.3 | Truth table | of half-subtracto |

|----------------------------------------|-----------|-------------|-------------------|

|----------------------------------------|-----------|-------------|-------------------|

| In           | puts            | Out             | puts                       |

|--------------|-----------------|-----------------|----------------------------|

| Minuend<br>X | Subtrahend<br>Y | Difference<br>D | Borrow<br>B <sub>out</sub> |

| 0            | 0               | 0               | 0                          |

| 0            | 1               | 1               | 1                          |

| 1            | 0               | 1               | 0                          |

| 1            | 1               | 0               | 0                          |

From Table 5.3, as discussed earlier, the Boolean expressions for difference (*D*) and Borrow out  $(B_{out})$  can be written as follows:

$$D = \overline{X}Y + X\overline{Y} = X \oplus Y$$

$$B_{out} = \overline{X}Y$$

From the above equations, the half-subtractor can be implemented using an Ex-OR gate, a NOT gate and an AND gate as shown in Fig. 5.6(b).

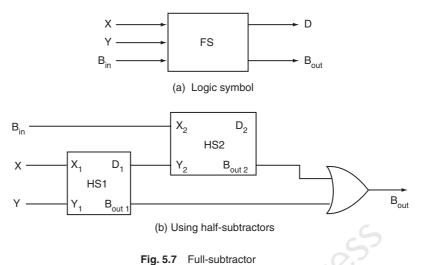

# 5.7 Full-subtractor

A full-subtractor is a combinational circuit that performs subtraction involving three bits, namely minuend bit, subtrahend bit and the borrow from the previous stage. The logic symbol for full-subtractor is shown in Fig. 5.7(a).

It has three inputs, X (minuend), Y (subtrahend) and  $B_{in}$  (borrow from previous stage), and two outputs D (difference) and  $B_{out}$  (borrow out). The truth table for the full-subtractor is given in Table 5.4. The full-subtractor can be implemented using two half-subtractors and an OR gate as shown in Fig. 5.7(b).

Arithmetic Circuits 179

Table 5.4

Truth table of full-subtractor

|             | Inputs         |                 | Out        | puts       |

|-------------|----------------|-----------------|------------|------------|

| Minuend bit | Subtrahend bit | Borrow in       | Difference | Borrow out |

| <u>X</u>    | Y              | B <sub>in</sub> | D          | out        |

| 0           | 0              | 0               | 0          | 0          |

| 0           | 0              | 1               | 1          | 1          |

| 0           | 1              | 0               | 1          | 1          |

| 0           | 1              | 1               | 0          | 1          |

| 1           | 0              | 0               | 1          | 0          |

| 1           | 0              | 1               | 0          | 0          |

| 1           | 1              | 0               | 0          | 0          |

| 1           |                | 1               | 1          | 1          |

From Table 5.4, the Sum of Product expression for the difference (D) output can be written as:

$$D = \overline{X} \overline{Y} B_{\text{in}} + \overline{X} \overline{Y} \overline{B_{\text{in}}} + X \overline{Y} \overline{B_{\text{in}}} + X \overline{Y} B_{\text{in}}$$

Simplifying the above expression,

$$D = (\overline{X} \,\overline{Y} + XY)B_{in} + (\overline{X}Y + X\overline{Y})\overline{B_{in}}$$

$$= (\overline{X \oplus Y})B_{in} + (X \oplus Y)\overline{B_{in}}$$

$$D = X \oplus Y \oplus B_{in}$$

Similarly, the sum of product expression for  $B_{out}$  can be written from the truth table as:

$$B_{\text{out}} = \overline{X} \overline{Y} B_{\text{in}} + \overline{X} \overline{Y} \overline{B_{\text{in}}} + \overline{X} \overline{Y} B_{\text{in}} + \overline{X} \overline{Y} B_{\text{in}}$$

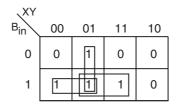

The equation for  $B_{out}$  can be simplified using Karnaugh map as shown in Fig. 5.8.

Fig. 5.8 K-map for B<sub>out</sub>

Now,  $B_{out} = \overline{X}Y + \overline{X}B_{in} + YB_{in}$

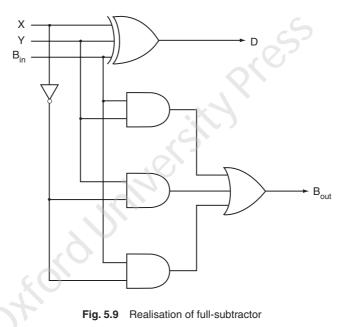

Using the above simplified expressions, the full-subtractor can be realised as shown in Fig. 5.9.

One can notice that the equation for D is the same as the sum output for a full-adder, and the borrow output  $B_{out}$  resembles the carry output for full-adder except that one of the inputs is complemented. From these similarities, it is possible to convert a full-adder into a full-subtractor by merely complementing that input prior to its application to the input of gates which form the borrow output.

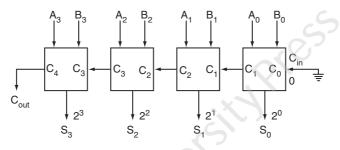

# 5.8 Parallel Binary Adder

In most logic circuits, addition of more than 1-bit is carried out. For example, modern computers and calculators use numbers ranging from 8 to 64-bits. The addition of multibit numbers can be accomplished using several full-adders. The 4-bit adder using full-adder circuits is capable of adding two 4-bit numbers resulting in a 4-bit sum and a carry output as shown in Fig. 5.10. Since all the bits of the augend and addend are fed into the adder circuits simultaneously and the additions in each position are taking place at the same time, this circuit is known as *parallel adder*.

181

The addition operation is illustrated in the following example: Let the 4-bit words to be added be represented by  $A_3A_2A_1A_0 = 111$  and  $B_3B_2B_1B_0 = 0011$ .

| Significant place |   | 4 | 3 | 2 | 1 |      |

|-------------------|---|---|---|---|---|------|

| Input carry       |   | 1 | 1 | 1 | 0 |      |

| Augend word A:    |   | 1 | 1 | 1 | 1 |      |

| Addend word B:    | _ | 0 | 0 | 1 | 1 | _    |

|                   | 1 | 0 | 0 | 1 | 0 | ←Sum |

|                   | ↑ |   |   |   |   | -    |

| Output carr       | у |   |   |   |   |      |

Addend and augend inputs

Fig. 5.10 4-bit binary parallel adder

In a 4-bit parallel binary adder circuit, the input to each full-adder will be  $A_i$ ,  $B_i$  and  $C_i$ , and the outputs will be  $S_i$  and  $C_{i+1}$ , where 'i' varies from 0 to 3. Also, the carry output of the lower order stage is connected to the carry input of the next higher order stage. Hence, this type of adder is called *ripple-carry adder*.

In the least significant stage,  $A_0$ ,  $B_0$  and  $C_0$  (which is 0) are added resulting in Sum  $S_0$  and Carry  $C_1$ . This carry  $C_1$  becomes the carry input to the second stage. Similarly, in the second stage,  $A_1$ ,  $B_1$  and  $C_1$  are added resulting in  $S_1$  and  $C_2$ ; in the third stage,  $A_2$ ,  $B_2$  and  $C_2$  are added resulting in  $S_2$  and  $C_3$ ; in the fourth stage,  $A_3$ ,  $B_3$  and  $C_3$  are added resulting in  $S_3$  and  $C_4$  which is the output carry. Thus, the circuit results in a sum  $(S_3S_2S_1S_0)$  and a carry output  $(C_{out})$ .

Though the parallel binary adder is said to generate its output immediately after the inputs are applied, its speed of operation is limited by the carry propagation delay through all stages. In each full-adder, the carry input has to be generated from the previous full-adder which has an inherent propagation delay. The propagation delay  $(t_p)$  of a full-adder is the time difference between the instant at which the inputs  $(A_i, B_i \text{ and } C_i)$  are applied and the instant at which its outputs  $(S_i \text{ and } C_{i+1})$  are generated. Therefore, in a 4-bit binary adder, the output in LSB stage is generated only after  $t_p$  seconds. Similarly, the output in the second stage will be generated only after  $t_p$  seconds from the time the inputs are applied; the third stage will generate outputs only after  $3t_p$  seconds and the fourth stage will generate outputs only after  $4t_p = 4 \times 50$  ns = 200 ns. The magnitude of such delay is prohibitive for high-speed computers. However, there are several methods to reduce this delay.

One of the methods of speeding up this process is look-ahead carry addition which eliminates the ripple-carry delay. This method is based on the carry generate and the carry propagate functions of the full-adder.

This scheme utilises logic gates to look at the lower order bits of the augend and addend if a higher-order carry is to be generated. This requires extra circuitry for getting high speed adders. This is not a significant consideration with the present day availability of integrated circuits.

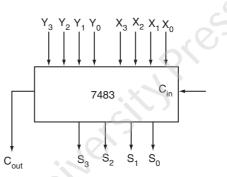

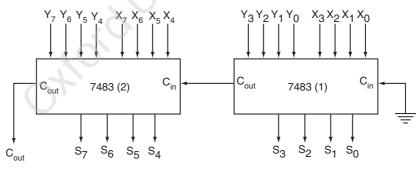

# 5.8.1 IC 7483—4-bit Parallel Binary Adder

The IC 7483 is a commonly available TTL 4-bit parallel binary adder chip. It contains four interconnected full-adders and a look-ahead carry circuitry for its operation. The logic symbol of IC 7483 is shown in Fig. 5.11(a). It has two 4-bit inputs,  $X_3X_2X_1X_0$  and  $Y_3Y_2Y_1Y_0$ , and, a carry input  $C_{in}$  in the LSB stage. The outputs are a 4-bit sum  $S_3S_2S_1S_0$  and a carry output  $C_{out}$  from the most significant bit stage.

(a) Logic symbol of IC 7483-4-bit parallel binary adder

(b) Cascading of two 7483 ICs

Fig. 5.11

Two or more parallel adder blocks can be connected in cascade to perform the addition operation on larger binary numbers. Fig. 5.11(b) shows the cascading connection of two 7483 adders. The four least significant bits of the numbers are added in the first adder. The carry output of this adder is given as the carry input to the second adder, which adds four most significant bits of the numbers. The output carry of the second adder is the final carry output.

# 5.8.2 4-bit Parallel Binary Subtractor

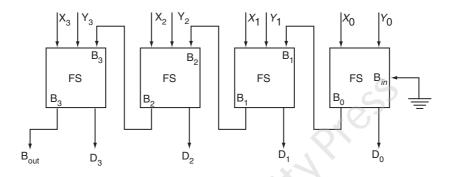

Just as a parallel binary adder can be implemented by cascading several full-adders, a parallel binary subtractor can also be implemented by cascading several full-subtractors. A 4-bit parallel binary subtractor that subtracts a 4-bit number  $Y_3 Y_2 Y_1 Y_0$  from another 4-bit number  $X_3 X_2 X_1 X_0$  is shown in Fig. 5.12. It has 4 difference outputs  $(D_3 D_2 D_1 D_0)$  and a borrow output  $(B_{out})$ . Note that the  $B_{in}$  of the LSB full-subtractor is connected to 0 and  $B_{out}$  of *i*th full-subtractor is connected to  $B_{in}$  of  $(i + 1)^{th}$  full-subtractor.

Fig. 5.12 4-bit parallel binary subtractor

# 5.9 Controlled Inverter

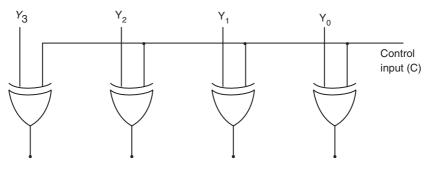

The subtraction of two binary numbers may be accomplished by taking the 2's complement of the subtrahend and adding to the minuend. By this procedure, the subtraction becomes an addition operation. The 2's complement of the subtrahend can be obtained by adding a 1 to the 1's complement of the subtrahend. From the Ex-OR gate truth table, we know that when one of the inputs is LOW the output is the true value of the other input and when one of the inputs is HIGH the output is the complement of the other input. Therefore, the complement of a binary digit can be obtained using an Ex-OR gate as shown in Fig. 5.13.

Fig. 5.13 Ex-OR gate functioning as an inverter

In Fig. 5.13, X is the input, C is the control input and Y is the output. From the figure, it is clear that if C = 0, then Y = X, i.e., input X is available at Y in uncomplemented form; if C = 1, then  $Y = \overline{X}$ , i.e., input X is available at Y in complemented form. Thus, if C = 1, the Ex-OR gate can function as an inverter. Similarly, a group of Ex-OR gates can be used to invert a group of bits. Fig. 5.14 shows the complementing process of a 4-bit binary number  $(Y_3 Y_2 Y_1 Y_0)$  using a controlled inverter.

When the control input is low, the output will be the input, i.e.  $Y_3 Y_2 Y_1 Y_0$ . When the control input is high, the output will be the complement of the input  $\overline{Y}_3 \overline{Y}_2 \overline{Y}_1 \overline{Y}_0$ .

Fig. 5.14 Controlled inverter

# 5.10 4-bit Parallel Adder/Subtractor

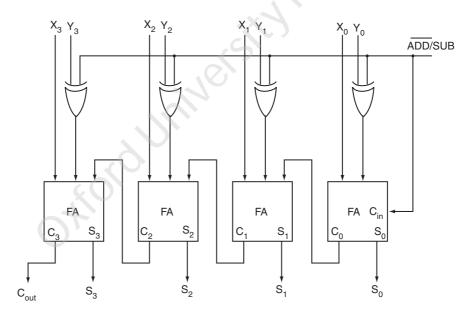

The 4-bit parallel binary adder/subtractor circuit shown in Fig. 5.15 performs the operations of both addition and subtraction. It has two 4-bit inputs  $X_3X_2X_1X_0$  and  $Y_3Y_2Y_1Y_0$ . The ADD/SUB control line, connected with  $C_{in}$  of the least significant bit of the full-adder, is used to perform the operations of addition and subtraction. The Ex-OR gates are used as controlled inverters.

Fig. 5.15 4-bit parallel adder/subtractor

To perform subtraction, the  $\overline{\text{ADD}}/\text{SUB}$  control input is kept high. Now, the controlled inverter produces the 1's complement of the addend  $(\overline{Y}_3 \overline{Y}_2 \overline{Y}_1 \overline{Y}_0)$ . Since 1 is given to  $C_{\text{in}}$  of the least significant bit of the adder, it is added to the complemented addend producing 2's complement of the addend before addition. Now, the data  $X_3 X_2 X_1 X_0$  will be added to the 2's complement of  $Y_3 Y_2 Y_1 Y_0$  to produce the Sum, i.e., the difference between the addend and the augend, and  $C_{\text{out}}$ , i.e., the borrow output of 4-bit subtractor. Also, it has  $S_3 S_2 S_1 S_0$  as sum output and  $C_{\text{out}}$  as carry output. When

$\overline{\text{ADD}}/\text{SUB}$  input is LOW, the controlled inverter allows the addend  $(Y_3 Y_2 Y_1 Y_0)$  without any change to the input of the full-adder, and the carry input  $C_{\text{in}}$  of least significant bit of full-adder, becomes zero. Now, the augend  $(X_3 X_2 X_1 X_0)$  and addend  $(Y_3 Y_2 Y_1 Y_0)$  are added with  $C_{\text{in}} = 0$ . Hence, the circuit functions as a 4-bit adder resulting in sum  $S_3 S_2 S_1 S_0$  and carry  $C_{\text{out}}$ .

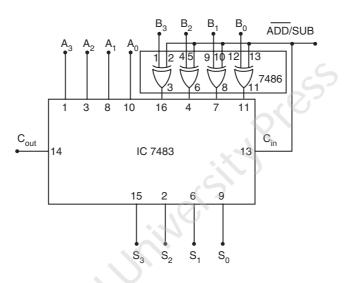

**Example 5.1** Construct a 4-bit parallel binary adder/subtractor using IC 7483.

*Solution* IC7483 is a 4-bit parallel binary adder. A 4-bit parallel binary adder/subtractor can be implemented using IC7483, controlled inverter IC7486 and a control line ADD/SUB as shown in Fig. E5.1.

Fig. E5.1 4-bit parallel binary adder/subtractor using IC 7483

# 5.11 Fast Adder

In the parallel binary adder discussed in section 5.7, the carry generated by the  $i^{\text{th}}$  adder is fed as carry input to the  $(i + 1)^{\text{th}}$  adder. In this adder, the output  $(C_{\text{out}} S_3 S_2 S_1 S_0)$  is available only after the carry is propagated through each of the adders i.e., from LSB to MSB adder through intermediate adders. Hence, the addition process can be considered to be complete only after the above carry propagation delay through adders, which is proportional to number of stages in it. One of the methods of making this process faster is look ahead carry addition, which eliminates the ripple carry delay. This method is based on the carry generating and the carry propagating functions of the full adder.

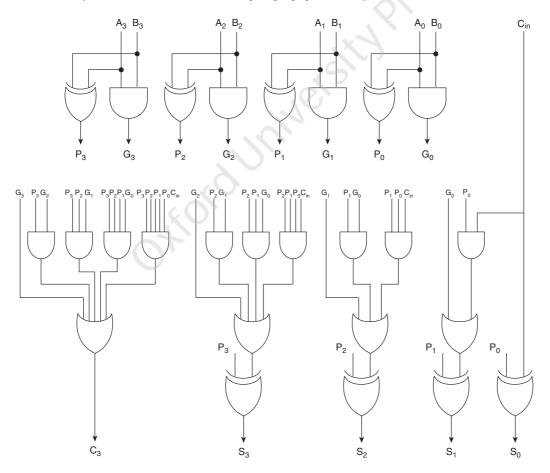

# 5.11.1 4-bit Carry Look Ahead Adder

The carry look ahead adder is based on the principle of looking at the lower order bits of the augend and addend if a high order carry is generated. This adder reduces the carry delay by reducing the number of gates through which a carry signal must propagate. To explain its operation, consider the truth table of full adder, shown in Table 5.5.

| Row | A | В | C <sub>in</sub> | S | Cout |                                                                                                                           |

|-----|---|---|-----------------|---|------|---------------------------------------------------------------------------------------------------------------------------|

| 0   | 0 | 0 | 0               | 0 | 0    | $) \rightarrow$ No carry generation                                                                                       |

| 1   | 0 | 0 | 1               | 1 | 0    | $\left\{ \rightarrow \begin{array}{l} \text{No carry generation} \\ \text{i.e. } C_{\text{out}} = 0 \end{array} \right\}$ |

| 2   | 0 | 1 | 0               | 1 | 0    |                                                                                                                           |

| 3   | 0 | 1 | 1               | 0 | 1    | Carry propagation                                                                                                         |

| 4   | 1 | 0 | 0               | 1 | 0    | $\begin{array}{c} \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\ \\$                                               |

| 5   | 1 | 0 | 1               | 0 | 1    |                                                                                                                           |

| 6   | 1 | 1 | 0               | 0 | 1    | $\left( \  \  \right)$ Carry generation                                                                                   |

| 7   | 1 | 1 | 1               | 1 | 1    | $\left\{ \rightarrow \begin{array}{c} \text{Carry generation} \\ \text{i.e. } C_{\text{out}} = 1 \end{array} \right\}$    |

| Table 5.5 | Truth table of Full adder. | emphasizing the conditions | s at which carry generation occurs |

|-----------|----------------------------|----------------------------|------------------------------------|

|           |                            |                            |                                    |

In rows 0 and 1, the carry output  $(C_{out})$  is always 'zero' and independent of carry input  $(C_{in})$ , while in rows 6 and 7, the  $C_{out}$  is always 'one' and independent of  $C_{in}$ . These are known as carry generate combinations. In rows 2, 3, 4 and 5 the carry output is equal to the carry input i.e.  $C_{out} = 1$  only when  $C_{in} = 1$ . These are carry propagate combinations. Let  $G_i$  represent the unity carry (i.e.  $C_{out} = 1$ ) generate condition and  $P_i$  represent the carry propagate condition of the  $i^{th}$  stage of a parallel adder.

From the Truth Table 5.5  $G_i$  is obtained by summing up the combinations corresponding to 6<sup>th</sup> and 7<sup>th</sup> rows as follows:

$$G_{i} = A_{i}B_{i}C_{in} + A B_{i}\overline{C_{in}}$$

$$= A_{i}B_{i}(C_{in} + \overline{C_{in}})$$

$$G_{i} = A_{i}B_{i}$$

Similarly the carry propagation condition ( $P_i$ ) occurs when either  $A_i = 1$  and  $B_i = 0$  or vice versa as shown in Truth Table 5.5. Now  $P_i$  is given by

$$P_i = A_i \overline{B}_i + \overline{A}_i B_i = A_i \oplus B_i$$

Consider the addition of two 4-bit binary numbers  $A(A_3A_2A_1A_0)$  and  $B(B_3B_2B_1B_0)$ . The unity carry output of the *i*<sup>th</sup> stage can be expressed in terms of  $G_i$ ,  $P_i$  and  $C_{i-1}$  which is the unity carry output of the (i-1)<sup>th</sup> stage as follows:

$$C_i(C_{out}) = G_i + P_i C_{i-1}$$

where  $C_{i-1}$  for LSB stage is  $C_{in}$  which is assumed to be zero. In a 4-bit binary adder, four stages of addition are required to add  $A_0B_0$ ,  $A_1B_1$ ,  $A_2B_2$  and  $A_3B_3$ . Therefore, for i = 0, 1, 2 and 3, the  $C_i$ 's are given by

0

$$\begin{array}{l} C_{0} &= G_{0} + P_{1} C_{in} \dots \text{ where } G_{0} = A_{0} B_{0}; P_{0} = A_{0} \oplus B_{0} \text{ and } C_{in} = \\ C_{1} &= G_{1} + P_{1} C_{0} \\ &= G_{1} + P_{1} (G_{0} + P_{0} C_{in}) \\ &= G_{1} + P_{1} G_{0} + P_{1} P_{0} C_{in} \dots \text{ where } G_{1} = A_{1} B_{1} \text{ and } P_{1} = A_{1} \oplus B_{1} \\ C_{2} &= G_{2} + P_{2} C_{1} \\ &= G_{2} + P_{2} (G_{1} + P_{1} G_{0} + P_{1} P_{0} C_{in}) \\ &= G_{2} + P_{2} G_{1} + P_{2} P_{1} G_{0} + P_{1} P_{0} C_{in} \dots \text{ where } G_{2} = A_{2} B_{2} \text{ and } P_{2} = A_{2} \oplus B_{2} \\ C_{3} &= G_{3} + P_{3} C_{2} \end{array}$$

Arithmetic Circuits 187

$$= G_3 + P_3(G_2 + P_2G_1 + P_2P_1P_0C_{in})$$

=  $G_3 + P_3G_2 + P_3P_2G_1 + P_3P_2P_1G_0 + P_3P_2P_1P_0C_{in}$  ..... where  $G_3 = A_3B_3$  and

$P_3 = A_3 \oplus B_3$

The sum of *A* and *B* is given by

$$S = C_3 S_3 S_2 S_1 S_0$$

where  $S_i = A_i \oplus B_i \oplus C_{i-1}$  for  $i = 0, 1, 2, 3$

i.e.,  $S_0 = A_0 \oplus B_0 \oplus C_{in}$

$S_1 = A_1 \oplus B_1 \oplus C_0$

$S_2 = A_2 \oplus B_2 \oplus C_1$

$S_3 = A_3 \oplus B_3 \oplus C_2$

Using the above equation, a 4-bit carry look ahead adder can be realized as shown in Fig. 5.16. From the diagram, one can easily understand that the addition of two 4 bit numbers can be done by a carry look ahead adder in a four gate propagation time. Also, it is important to note that the addition of n-bit binary numbers takes the same four gate propagation delay.

Fig. 5.16 Logic diagram of 4-bit carry look ahead adder

# 5.12 Serial Adder

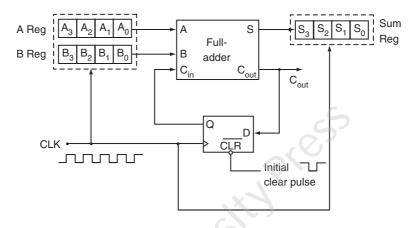

Though the parallel adder performs the addition of two binary numbers at a relatively faster rate, the disadvantage of the parallel addition is that it requires a large amount of logic circuitry. This increases in direct proportion with the number of bits in the numbers being added. On the other hand, in *serial addition*, the addition operation is carried out bit-by-bit. Therefore, the serial adder requires simpler circuitry than a parallel adder but results in a low speed of operation.

Fig. 5.17 4-bit serial adder

The diagram of a 4-bit serial adder is shown in Fig. 5.17. The two shift registers A and B are used to store the numbers to be added serially. A single full-adder is used to add one pair of bits at a time along with the carry. The D flip-flop, i.e. carry flip-flop, is used to store the carry output of the full-adder so that it can be added to the next significant position of the numbers in the registers. The contents of the shift registers shift from left to right and their outputs starting from  $A_0$  and  $B_0$  are fed into a single full-adder along with the output of the carry flip-flop upon application of each clock pulse.

The sum output of the full-adder is fed to the Most Significant Bit  $(S_3)$  of the sum register. For each succeeding clock pulse, the contents of both the shift registers are shifted once to the right, and new sum bit and new carry bit are transferred to sum register and carry flip-flop respectively. This process continues until all the pairs of bits are added.

The following example explains the operation of a serial adder. Let the augend  $(A_3A_2A_1A_0)$  be 0111 and the addend  $(B_3B_2B_1B_0)$  be 0010, stored in shift registers A and B respectively. Also, the carry flip-flop has been initially cleared to the 0 state, so that  $C_{in} = 0$ .

**First clock pulse** Before the first clock pulse occurs, as the inputs to the Full-adder are  $A_0 = 1$ ,  $B_0 = 0$  and  $C_{in} = 0$ . The full-adder outputs will be S = 1 and  $C_{out} = 0$ . When the first clock pulse occurs, the value in the A and B registers shift from left to right by one bit. In addition, the sum (S) is transferred to  $S_3$  of sum register, and the  $C_{out}$  is transferred to the carry flip-flop, whose output becomes 0, which is the carry input of the full-adder.

**Second clock pulse** Now,  $A_0 = 1$ ,  $B_0$  and  $C_{in} = 0$ , at the full-adder input. Therefore, S = 0 and  $C_{out} = 1$  When the second clock pulse occurs, A, B and sum registers again shift right; S = 0 is transferred to  $S_3$ , and  $C_{out} = 1$  is transferred to the carry flip-flop.

**Third clock pulse** The values of  $A_0$  and  $B_0$  are now 1 and 0 respectively, and  $C_{in}$  is 1. These values produce S = 0 and  $C_{out} = 1$  at the full-adder outputs. On the occurrence of the third clock pulse, the A, B and sum registers shift right, sum = 0 goes to  $S_3$ , and  $C_{out} = 1$  goes to the carry flip-flop.

**Fourth clock pulse** Both  $A_0$  and  $B_0$  are now zero, and  $C_{in} = 1$ . Therefore, the full-adder produces S = 1 and  $C_{in} = 0$ . The fourth clock pulse transfers S = 1 to  $S_3$  and initiates all the other transfers. At the end of this fourth clock pulse, the sum value (1001) will be available in the sum register, and  $C_{out}$  is 0.

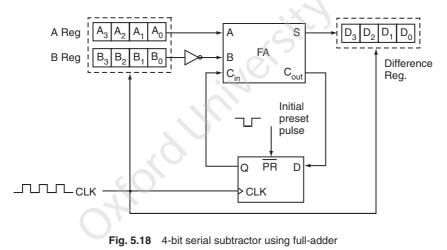

# 5.13 Serial Subtraction Using 2's Complement

A serial subtractor can be obtained by converting the serial adder of Fig. 5.17 using the 2's complement system. For subtraction, the subtrahend is stored in the *B* register and must be 2's-complemented before it is added to the minuend stored in the *A* register. One simple way to accomplish this is to complement the *B* register and to make the initial  $C_{in} = 1$  instead of 0 prior to the first clock pulse. This can be easily accomplished by feeding the inverted output  $\overline{B_0}$  into the full-adder instead of  $B_0$ and initially setting the carry flip-flop to 1 instead of clearing it. The remaining circuitry is the same as serial adder.

The circuit for 4-bit serial subtractor using full-adder is shown in Fig. 5.18.

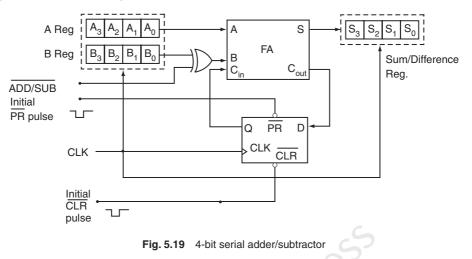

# 5.14 4-bit Serial Adder/Subtractor

A 4-bit serial adder/subtractor can be constructed in a manner similar to its parallel counterpart as shown in Fig. 5.19.

In the circuit shown in Fig. 5.19, when  $\overline{\text{ADD}}/\text{SUB} = 0$ , the uncomplemented  $B_3B_2B_1B_0$  will be applied to the full-adder. The carry flip-flop is initially cleared by applying a low pulse at  $\overline{\text{CLR}}$ input and the circuit thus functions as a 4-bit serial adder. When  $\overline{\text{ADD}}/\text{SUB} = 1$ , the complemented output of *B* register ( $\overline{B}_3\overline{B}_2\overline{B}_1\overline{B}_0$ ) will be applied to the full-adder. The carry flip-flop is initially set to 1 so as to get the 2's complement of the subtrahend by applying a low pulse at  $\overline{PR}$  input and thus the circuit functions as a 4-bit serial subtractor. The comparison of serial adder with parallel adder is shown in Table 5.5.

Table 5.5 Serial adder Vs parallel adder

| Serial adder                     | Parallel adder                                       |

|----------------------------------|------------------------------------------------------|

| Serial adder is less fast        | Parallel adder is generally faster                   |

| It requires fewer components     | It requires more components compared to serial adder |

| Addition is performed bit by bit | All the bits are added simultaneously                |

| starting from the LSB            |                                                      |

# 5.15 BCD Adder

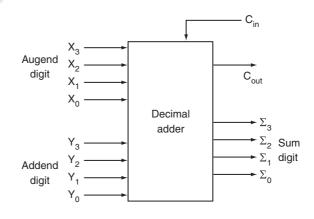

A BCD adder is a circuit that adds two BCD digits in parallel and produces a sum digit which is also in BCD. A BCD adder must include the correction logic in its internal construction. A block diagram for the BCD adder is shown in Fig. 5.20. This adder has two 4-bit BCD inputs  $X_3 X_2 X_1 X_0 Y_3 Y_2 Y_1 Y_0$  and a carry input ( $C_{in}$ ). It also has a 4-bit sum output ( $\Sigma_3 \Sigma_2 \Sigma_1 \Sigma_0$ ) and a carry output ( $C_{out}$ ). Here, the sum output is also in BCD form.

Fig. 5.20 Block diagram of a BCD adder

© Oxford University Press. All rights reserved.

A BCD adder circuit must be able to do the following:

- 1. Add two 4-bit BCD numbers using straight binary addition.

- 2. If the four-bit sum is equal to or less than 9, the sum is in proper BCD form and no correction is needed.

- 3. If the four-bit sum is greater than 9 or if a carry is generated from the sum, the sum is not in the BCD form. Then, the digit 6 (0110) should be added to the sum to produce the BCD results. The carry may be produced due to this addition and it is added to the next decimal position.

Table 5.6 shows the results of BCD addition with corrections indicated.

| Decimal | 1                     | Uncorre                       | cted B    | CD Sun | n            |      |       | Correc | ted BC | D Sum        |            |

|---------|-----------------------|-------------------------------|-----------|--------|--------------|------|-------|--------|--------|--------------|------------|

| digit   | <i>C</i> <sub>3</sub> | $S_3$                         | $S_2$     | $S_1$  | $S_{\theta}$ | Cout | $S_3$ | $S_2$  | $S_1$  | $S_{\theta}$ |            |

| 0       |                       | 0                             | 0         | 0      | 0            |      | 0     | 0      | 0      | - 0          |            |

| 1       |                       | 0                             | 0         | 0      | 1            |      | 0     | 0      | 0      | 71           |            |

| 2       |                       | 0                             | 0         | 1      | 0            |      | 0     | 0      | 1      | 0            |            |

| 3       |                       | 0                             | 0         | 1      | 1            |      | 0     | 0      | 1      | 1            | No         |

| 4       |                       | 0                             | 1         | 0      | 0            |      | 0     | 1      | 0      | 0            | correction |

| 5       |                       | 0                             | 1         | 0      | 1            |      | 0     | 1      | 0      | 1            | required   |

| 6       |                       | 0                             | 1         | 1      | 0            |      | 0     | 1      | 1      | 0            |            |

| 7       |                       | 0                             | 1         | 1      | 1            |      | 0     | 1      | 1      | 1            |            |

| 8       |                       | 1                             | 0         | 0      | 0            | .0   | 1     | 0      | 0      | 0            |            |

| 9       |                       | 1                             | _0_       | 0      | 1            | 1 C  | 1     | 0      | _0_    | 1            |            |

| 10      | = = = =               | 1                             | = = = = = | 1      | = = = = :    | 1    | 0     | 0      | 0      | 0            |            |

| 11      |                       | 1                             | 0         | 1      | 11           | 1    | 0     | 0      | 0      | 1            |            |

| 12      |                       | 1                             | 1         | 0      |              | 1    | 0     | 0      | 1      | 0            |            |

| 13      |                       | 1                             | 1         | 0      | 1!           | 1    | 0     | 0      | 1      | 1            |            |

| 14      |                       | 1                             | 1         |        |              | 1    | 0     | 1      | 0      | 0            | Correction |

| 15      |                       | 1                             | .1        | 1      | 1            | 1    | 0     | 1      | 0      | 1            | required   |

| 16      | [īī]                  |                               | 0         | 0      | 0            | 1    | 0     | 1      | 1      | 0            | -          |

| 17      | 111                   | 0                             | -0        | 0      | 1            | 1    | 0     | 1      | 1      | 1            |            |

| 18      |                       | 0                             | 0         | 1      | 0            | 1    | 1     | 0      | 0      | 0            |            |

| 19      | 111                   | 0                             | 0         | 1      | 1            | 1    | 1     | 0      | 0      | 1            |            |

|         |                       |                               | -         |        |              |      |       | -      | -      |              |            |

|         |                       |                               |           |        |              |      |       |        |        |              |            |

|         |                       | . 9                           | $S_3S_2$  |        |              |      |       |        |        |              |            |

|         |                       | S <sub>1</sub> S <sub>0</sub> |           | 01     | 11           | 10   |       |        |        |              |            |

|         |                       |                               |           |        | (12)         |      |       |        |        |              |            |

|         |                       | U                             | 0         |        |              |      |       |        |        |              |            |

|         |                       | 0                             | 1         |        | 13           |      |       |        |        |              |            |

|         |                       | 1                             | 1         |        | /15          | 11)  |       |        |        |              |            |

|         |                       |                               |           |        |              |      |       |        |        |              |            |

|         |                       | 1                             | 0         |        | ((14)        | 10廾  |       |        |        |              |            |

Table 5.6

Results of BCD addition with corrections indicated

Fig. 5.21 K-map simplification

© Oxford University Press. All rights reserved.

$C_n = \underbrace{S_3 S_2}_{} + \underbrace{S_3 S_1}_{} + C_3 - \ldots$

From the Table 5.6, it is clear that correction is required. When the sum output  $(S_3S_2S_1S_0)$  is greater than 9, i.e., when  $C_3 = 1$  (OR)  $S_3 = 1$  (AND)  $[S_2 = 1$  (OR)  $S_1 = 1$ ], add 0110 to get the BCD result. Note that when  $C_3 = 1$ , the result is 16 and above; when  $S_3 = 1$  (AND)  $S_2 = 1$ , the result is 12 and above; when  $S_3 = 1$  (AND)  $S_1 = 1$ , the result is 10 and above; when  $S_3 = 1$  (AND)  $[S_2 = 1$  (OR)  $S_1 = 1$ ], the result is 14 and above. Therefore, the condition for correction can be written as an expression as follows:

$$C_n = C_3 + S_3(S_2 + S_1)$$

Alternatively, the above condition for correction can also be obtained by *K*-map method as shown in Fig. 5.21.

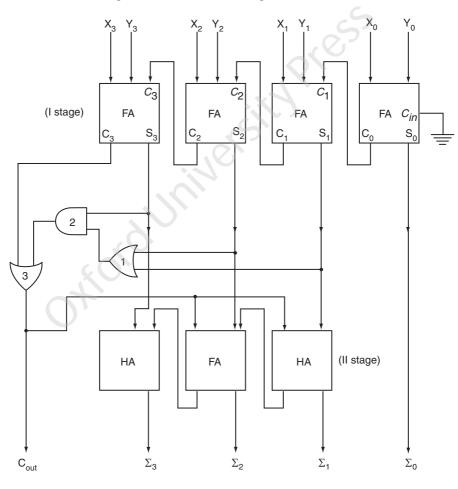

As discussed above, a BCD adder must be capable of adding two 4-bit BCD numbers, and the result has to be corrected to BCD, if the above condition is satisfied, by adding 0110. The circuit diagram for BCD adder using full-adders is shown in Fig. 5.22.

Fig. 5.22 BCD adder using full-adders

The operation of BCD adder shown in Fig. 5.22 is explained as follows: the first stage of full-adders adds two 4-bit BCD numbers, and its sum  $(S_3 S_2 S_1 S_0)$  and carry  $(C_3)$  are checked to

ascertain whether the result exceeds 9 by AND-OR gate combinations. If the output of OR gate (3) is equal to 1, then correction is required and this is accomplished by adding 0110 in the second stage of adders as shown in Fig. 5.22. Now, the BCD result is  $\Sigma_3 \Sigma_2 \Sigma_1 \Sigma_0$  with carry output ( $C_{out}$ ).

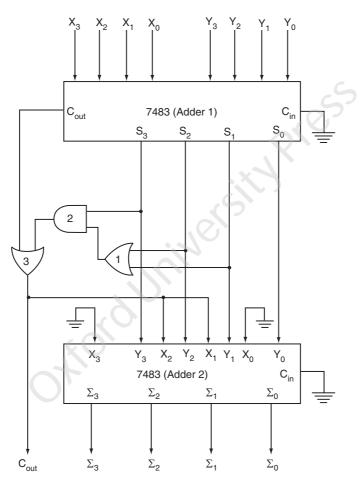

The BCD adder can also be implemented using two 7483 ICs as shown in Fig. 5.23. Here,  $X_3X_2X_1X_0$  and  $Y_3Y_2Y_1Y_0$  are the BCD inputs. The outputs of adder 1 ( $S_3S_2S_1S_0$  and  $C_{out}$ ) are checked to ascertain whether the output is greater than 9 by AND-OR gate combinations. If correction is required, then a 0110 is added with the output of adder 1. Now, the adder 2 output forms the BCD result ( $\Sigma_3\Sigma_2\Sigma_1\Sigma_0$ ) with carry output ( $C_{out}$ ).

Fig. 5.23 BCD adder using 7483 ICs

# 5.16 Binary Multiplier

Multiplication operation can be carried out by (i) Multipliers using partial product addition and shifting and (ii) Parallel multipliers.

# 5.16.1 Multiplier using Shift Method

To understand the multiplication process using shift method, consider the multiplication of two 4-bit binary numbers 1010 and 1011, as an example.

| 1010    | $\rightarrow$ | Multiplicand      |

|---------|---------------|-------------------|

| × 1011  | $\rightarrow$ | Multiplier        |

| 1010    | $\rightarrow$ | Partial product 1 |

| 1010    | $\rightarrow$ | Partial product 2 |

| 0000    | $\rightarrow$ | Partial product 3 |

| 1010    | $\rightarrow$ | Partial product 4 |

| 1101110 |               |                   |

From the above multiplication process, one can easily understand that if the multiplier bit is 1, then the multiplicand is simply copied as a partial product; if the multiplier bit is 0, then the partial product is 0. Whenever a partial product is obtained, it is shifted one bit to the left of the previous partial product. This process is continued until all the multiplier bits are checked, and then the partial products are added. This multiplication process, i.e. multiplication by partial product addition and shifting, can be implemented using the block diagram shown in Fig. 5.24.

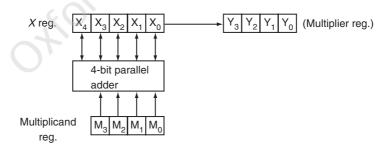

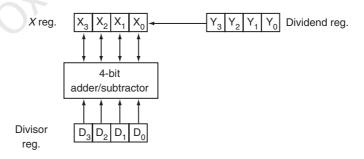

In the diagram shown in Fig. 5.24, the 4-bit multiplier is stored in register  $Y(Y_3Y_2Y_1Y_0)$ ; the 4-bit multiplicand is stored in register  $M(M_3M_2M_1M_0)$ , and the X register  $(X_4X_3X_2X_1X_0)$  is initially cleared to 00000. Here, to perform multiplication, the least significant bit of the multiplier bit  $(Y_0)$  is checked whether it is 0 or 1. If  $Y_0 = 1$ , the number in the multiplicand register (M) is added with the least significant 4-bits of X register  $(X_3X_2X_1X_0; X_4$  is to store carry in addition process) and the combined X and Y register is shifted to the right by 1 bit. If  $Y_0 = 0$ , the combined X and Y register is shifted to the right by 1 bit. If  $Y_0 = 0$ , the combined X and Y register is shifted to the rultiplication. This process has to be repeated four times to perform 4-bit multiplication. Now, the multiplication result  $(R_7R_6R_5R_4R_3R_2R_1R_0)$  will be available in X and Y registers  $(X_3X_2X_1X_0Y_3Y_2Y_1Y_0)$ .

Fig. 5.24 4-bit binary multiplier using shift method

#### 5.16.2 Parallel Multiplier

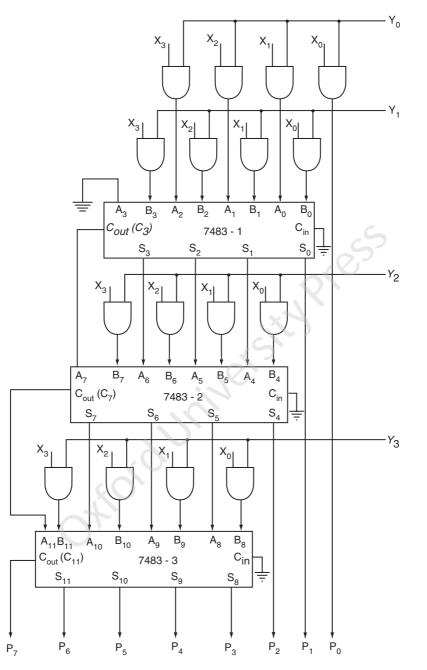

The 4-bit multiplier using shift method requires 4 cycles of addition and shifting operations, but it requires only a single 4-bit parallel adder. The speed of multiplication process can be increased considerably in parallel multiplier at the extra cost of increased hardware. The circuit diagram for a 4-bit parallel multiplier is shown in Fig. 5.25.

Arithmetic Circuits

Fig. 5.25 4-bit parallel multiplier

It requires three 4-bit parallel binary adders and 16 numbers of 2-input AND gates. Here, each group of 4 AND gates is used to obtain partial products while 4-bit parallel adders are used to add the partial products. Since the generation of partial products and their additions are performed in parallel in the group of AND gates and 4-bit adders respectively, the multiplication result

© Oxford University Press. All rights reserved.

$(P_7P_6P_5P_4P_3P_2P_1P_0)$  will be available at the output immediately after the propagation delay in the multiplier circuit.

The operation of the parallel multiplier can be understood in a better manner from the symbolic form of binary multiplication process shown in Fig. 5.26.

|                                               | •                             | X <sub>2</sub><br>Y <sub>2</sub> |                | •              | Multiplicand<br>Multiplier   |

|-----------------------------------------------|-------------------------------|----------------------------------|----------------|----------------|------------------------------|